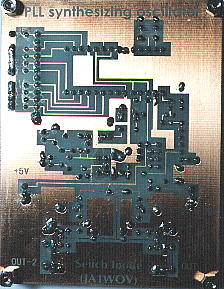

PLL synthesizing oscillator (2)

Block diagram of the top is a clickable image map. You can jump to each page of the explanation when you click each block. |

|

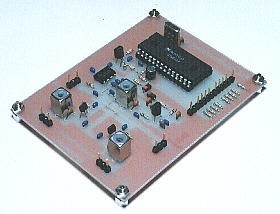

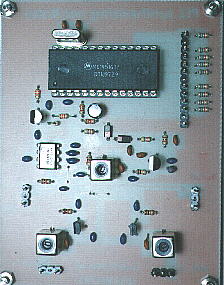

In this page, I introduce the PLL synthesizer oscillator which used MC145163. As for the operation principle of the PLL synthesizer oscillator, see "Principle of the PLL oscillator". This IC for the PLL can specify a dividing ratio directly with the BCD. The output of the BCD counter can be directly connected. There is not a serial data generator, being necessary. It makes a frequency 145 - 10.7 = 134.3MHz in the purpose to use at the 145MHz band of the amateur radio. 10.7MHz are an intermediate frequency in the FM. MC145163 can not handle a 130MHz frequency directly. Because it is, it is inputting to MC145163 after lowering a frequency to 15MHz using the outside oscillator. The outside oscillator is good with the crystal oscillator but is using a PLL oscillator to suppress a frequency change to the utmost. It is using a 10.24MHz crystal oscillator for the reference frequency of MC145163. It divides it to 1/1024 and it makes 10KHz a phase comparison frequency. The output frequency can be changed in the 10KHz unit by the specification of the dividing ratio. |