Yes, I know I skipped September, it is still in the works but having digital camera issues. I can't seem to get good closeups. Does anyone know how to adapt a macro lens to an HP Photosmart 435?

I will have December out asap, just a bit of editing and an animation to finish up.

In this issue:

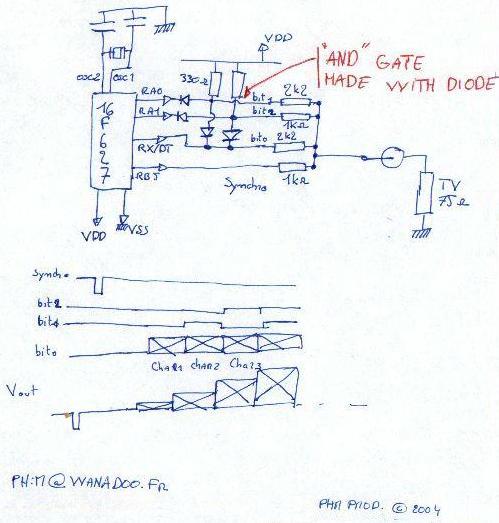

First a character based video terminal circuit idea that is implemented with a PIC 16F627 using the hardware USART to shift out character pixels. This allows for the much slower running PIC to still generate a 16*10 char display with 64, 8x8 pixel characters. Yes, an SX or other high speed processor could bit bang it, but shift register chips are cheap and allow for that much more processing or lower clock speed (and lower power, heat, etc...). For more details (in French) see the authors site at : http://perso.wanadoo.fr/phmworld Bablefish does pretty well with it.

Other than the idea of using a USART, I really like the diode AND gate in the D2A converter which allows 4 levels of grey on the display. Because of the slow processor, he can only change the grey level between character, but that is all he needs right?

See also:

| IBM's official method of recognizing their original EGA graphics card was to look for the string "IBM, Inc." (or something like that) at a certain address in the card's ROM. 3rd party EGA cards simply put "Not a product of " in front of it - satisfying the protocol, without committing a copyright violation. |

Just because we CAN bit bang doesn't mean that was always MUST. If a bit of external logic allows us to get even more done, why not use it? Here is a circuit idea for an SX plus shift register video terminal. I think you could get to 80 by 24 pretty easily with this. Of course, that requires a text memory of 1920 bytes, but we should have enough time left over to read an external RAM.

SX

+-------------------------+

| |

+------------------------------|> |

| | |

| +------------+-------------|A0 |

| | | ___ | |

| | +-| \ | |

| | -------- | )O--+ | |

| +---|D Q|---|__/ | | B0 B1 B2 B3 B4 B5 B6 B7 |

| | | '00 | +-------------------------+

+--|>O--|> Q*| | | | | | | | | |

| '04 -------- | | | | | | | | |

| 74HC74 | | | | | | | | |

| | +-------------------------+

| +--------------+ | | D0 D1 D2 D3 D4 D5 D6 D7 |

| | | | | |

| | -------- | +--O|PE |

| +---|D Q| | | |

+------+ | | | | | |

| 13.8 |--+-------|> Q*|---+-----------|> Q7 |----> to

| MHz | -------- | | video

+------+ 74HC74 +-------------------------+

74HC166

Add'l circuitry to generate blanking and sync from PIC outputs not shown. The '04 inverter can obviously be replaced with another NAND gate from the '00. Or all the 74HC stuff can be put into one CPLD.

One flip-flop is used to divide the oscillator clock to get the shift clock. The other is used together with the gates to produce a parallel load enable for the shift register. The parallel enable needs to be only one dot clock wide, but the narrowest pulse the firmware can produce on a port pin is two dot clocks wide. The firmware generates a two dot clock wide positive-going pulse, we use a flip-flop to delay it one dot clock, then NAND it with the undelayed pulse producing a negative pulse one dot clock wide. The inverter on the flip-flop clock is to make it negative-edge-triggered, so that the parallel load enable of the shift register will be stable during its clock input transition (rising edge).

The code to generate the active video is an unrolled look like this:

mov W, buf+0

mov Rb, W

setb Ra.0 ; pulse load input to shift register

clrb Ra.0

mov W, buf+1

mov Rb, W

setb Ra.0 ; pulse load input to shift register

clrb Ra.0

; repeat 42 more times using successive bytes of the buffer

mov W, buf+44

mov Rb, W

setb Ra.0 ; pulse load input to shift register

clrb Ra.0

mov W, #0 ; generate black the rest of the time

mov Rb, W

setb Ra.0 ; pulse load input to shift register

clrb Ra.0

If we must bitbang, how do we do it? Here is the standard methods followed by some "tricks"

The most obvious way to get a really fast shift register is to just rotate the bits in a port. Of course, you have to set every pin to output and leave them unconnected. It wastes an entire port, but it does have the advantage of being bloody fast. Since each pin's state must be read back into the uC before it can be shifted and sent out to the next pin, Read / Modify / Write problems are a possibility. For example, if B.7 is set and B.6 is cleared, then when you rotate the port right, the 1 from B.7 is applied to B.6. But things don't happen instantly, not even in a 75MIPS processor! As the port starts to drive B.6 high, if another shift is performed before it makes it above the point that defines a logical one, B.6 will be read as a 0! The result is that B.5 will be set low after this second shift and will loose the bit that was originally set in B.7.

The sample code I'm going to paste in here is from a high speed UART application, and the bit of code before the actuall rotating of the port is so neat I'm going to leave it in, even though it doesn't really relate to video applications.

;PORT B, bit0 is the data output bit. All other port bits are ;configured as outputs, but are otherwise wasted ; pre-calculate the parity. mov W, >>parity ;Put Parity into Carry mov W, data clr RB ;start bit mov RB, W ;d0 rr RB ;d1 and pick up the parity bit rr RB rr RB etc...

This gives only 2 cycle per bit which is quite fast and doesn't waste any port pins. It can cause Read / Modify / Write problems however, so it would be best if the other port pins are unused or inputs.

mov W, >>DATA ;reformat data to have:

xor DATA, W ; 1 = bit change

; 0 = no bit change

;

mov W, #(1<<S_PIN) ;W = serial pin mask

clrb S_PORT.S_PIN ;start bit

snc ;bit 0

xor S_PORT, W ;

snb DATA.0 ;bit 1

xor S_PORT, W ;

snb DATA.1 ;bit 2

xor S_PORT, W ;

snb DATA.2 ;bit 3

xor S_PORT, W ;

snb DATA.3 ;bit 4

xor S_PORT, W ;

snb DATA.4 ;bit 5

xor S_PORT, W ;

snb DATA.5 ;bit 6

xor S_PORT, W ;

snb DATA.6 ;bit 7

xor S_PORT, W ;

nop ;delay

setb S_PORT.S_PIN ;stop bit = 1

ret

This one is unique in that as long as the remaining 3 bits of RA are set to input, no pins are wasted AND it can't cause Read / Modify / Write problems!

rr data ;Get new bit from RAM rl RA ;Rotate C into A.0 rr data rl RA ;etc...

This code generats character video using the lower 4 pins of RA as a shift register. RA.0 is the output, but RA.1 - RA.3 must be set to outputs and left unconnected. Each entry in the character generator table needs to have bits 8..11 (the top 4 bits of the 12 bit word) set to the top 4 bits of the address of that word so that when M is loaded by the IREAD, its value is retained.

mov RowCout, #Rows

:RowLoop

mov RowScanLine, #(ScanLines/Rows)

;if you wanted to, you could skip a line of video here (between

;rows) and use the time to load a row of character data from

;external RAM or FRAM

:ScanLineLoop

jnb HorzSync, $ ;wait for the Horizontal sync.

mov ColCount, #Cols

mov w, ScanLine ;high pointer into the character generator table

mov m, w ;(which character pixel row)

mov w, ind ;low pointer into the table (which character)

iread

:CharScanLoop

mov ra, w

mov DataHi, W

rr ra

inc fsr

rr ra

setb fsr.4

rr ra

mov w, <>DataHi

mov ra, w

mov w, ind

rr ra

iread

rr ra

dec ColCount

rr ra

jnz :CharScanLoop

;An extra cycle or 2 here just spaces the characters a bit more.

djnz RowScanLine, :ScanLineLoop

djnz RowCount, :RowLoop

VGA is actually actually just about the same as standard NTSC, just some different timings, and three seperate color inputs.

There are three signals -- red, green, and blue -- that send color information to a VGA monitor. These three signals each drive an electron gun that emits electrons which paint one primary color at a point on the monitor screen. Analog levels between 0 (completely dark) and 0.7 V (maximum brightness) on these control lines tell the monitor what intensities of these three primary colors to combine to make the color of a dot (or pixel) on the monitor’s screen.

Technically VGA video has 480 lines and each line usually contains 640 pixels. In order to paint a frame, we require two synchronization signals in order to start and stop the deflection circuits at the right times. The timing for the VGA synchronization signals is shown here.

Negative pulses on the horizontal sync signal demark the start and end of a line. The actual pixels are sent to the monitor within a 25.17 ms window. The horizontal sync signal drops low a minimum of 0.94 ms after the last pixel and stays low for 3.77 ms. A new line of pixels can begin a minimum of 1.89 ms after the horizontal sync pulse ends. So a single line occupies 25.17 ms of a 31.77 ms interval. The other 6.6 ms of each line is the horizontal blanking interval.

In an analogous fashion, negative pulses on a vertical sync signal demark the start and end of a frame made up of video lines. The lines are sent to the monitor within a 15.25 ms window. The vertical sync signal drops low a minimum of 0.45 ms after the last line and stays low for 64 ms. The first line of the next frame can begin a minimum of 1.02 ms after the vertical sync pulse ends. So a single frame occupies 15.25 ms of a 16.784 ms interval. The other 1.534 ms of the frame interval is the vertical blanking interval.

This simple software makes a color bar or cross-hatch pattern on PC VGA or SVGA monitor. Its very simple just look at the circuit for all pin definitions.

The pins ra.0 to ra.2 are the respective outs for blue, red and green signals, and rb.0 and rb.1 the sync H and V. The rb.3 pin is used to change the mode, from bars, to cross-hatch.

Really, there is not too much that I can say about the project; the SX software generates all the signals, keeping count of the clock cycles. Look at the code and you'll have a better idea of how it works.

I'm using it to test many monitors, and it gives me a good result. I have found that in some cheap Samsung or Goldstar monitors there is a difference in the V size.

You can put

it all together in a little box to bring it with you in your pocket.

You can put

it all together in a little box to bring it with you in your pocket.

Good Luck !

;***************************************************************************************** ; ; Filename: VGA Monitor tester.src ; ; Author: Alberto Geraci ; BTX Sistemas ; Argentina. ; ; Revision: 1.01 ; ; Freq: 50MHz ; ; Compiled using: SX-Key. ; ; Date Written : January 16, 2002 ; ; Last Revised : January 25, 2002 ; ; Program Description: ; ; Super Simple !! VGA Monitor tester ; Simple project to demostrate the SX power running at 50Mhz ; It generates color bars and white lines in 640x480 mode. ; ; Interface Pins: ; ; azul = ra0 = pin 1 ; rojo = ra1 = pin 3 ; verde= ra2 = pin 2 ; ; H sync = rb0 = pin 13 ; V sync = rb1 = pin 14 ;***************************************************************************************** ; DEVICE SX18L,OSCHS3,TURBO,stackx_optionx,protect RESET Start FREQ 50_000_000 counter equ $08 repeat equ $09 times equ $0A lazo equ $0B Start mov ra, #%00000000 mov !ra,#%11110000 mov rb, #%00000011 mov !rb,#%00001000 mov w,#$0E mov M,w mov !rb,#%11110111 mov w,#$0F mov M,w org 20 ; ; MACROS ; ;*** MACRO VSYNC **************************************************************************************** vsync MACRO ;3180 cycles ; 63.6 uSeg ;; 28 + 3.8 + 28 + 3.8 ;;1400+190+1399+191 ;********** PULSO DE SINCRO V ******************************************************************* clrb rb.1 ; 1 cycle ; bit 6 low (Vertical sync pulse begins) mov counter,#174 ; 2 cycles :pupV1 nop nop ; 1 cycle nop ; 1 cycle decsz counter ; 1 cycle ; jmp @:pupV1 nop ; 1 cycle nop ; 1 cycle nop ; 1 cycle ;********** PULSO DE SINCRO H ******************************************************************* clrb rb.0 ; 1 cycle ; bit 6 low (Horizontal sync pulse begins) mov counter,#38 ; 2 cycles :pupH2 decsz counter ; 1 cycle ; jmp @:pupH2 ; 4 cycles ; setb rb.0 ; 1 cycle ; bit 6 high (Horizontal sync pulse finishes) ;************************************************************************************************ mov counter,#175 ; 2 cycles :pupV2 nop nop ; 1 cycle nop ; 1 cycle decsz counter ; 1 cycle ; jmp @:pupV2 ; 4 cycles ;********** PULSO DE SINCRO H ******************************************************************* clrb rb.0 ; 1 cycle ; bit 6 low (Horizontal sync pulse begins) mov counter,#38 ; 2 cycles :pupH3 decsz counter ; 1 cycle ; jmp @:pupH3 ; 4 cycles ; ;************************************************************************************************ mov rb,#%00000011 ; 2 cycles ;************************************************************************************************ ENDM ;******************************************************************************************************** ;******************************************************************************************************** Barras ; ****** now I must make front porch vertical ************************************** mov times,#2 jtama call @linea_vac2 decsz times ; when I finish I leave losing 5 cycles decsz and of ret jmp @jtama ; *********************************************************************************************** ; ****** now I must make vertical sync ************************************************ vsync ; *********************************************************************************************** ; ****** ahora tengo que hacer 33 lineas de portico superior y comienzo ************************* ; ****** now I must make 33 lines of high porch and beginning mov times,#19 jmp @jcc jcc nop nop jtama2 call @linea_vac decsz times ; when I finish I leave losing 5 cycles decsz and of ret jmp @jtama2 ; *********************************************************************************************** ; ****** ahora tengo que hacer 240 lineas de video ********************************************* ; ****** now I must make 240 lines of video ********************************************* mov times,#254 nop jtama3 call @linea decsz times ; ; when I finish I leave losing 5 cycles decsz and of ret jmp @jtama3 ; *********************************************************************************************** ; ****** ahora tengo que hacer 8 lineas de parte inferior de pantalla ************************** ; ****** now I must make 8 lines at lower part of screen ************************** mov times,#8 nop jtama5 call @linea_vac decsz times ; ; when I finish I leave losing 5 cycles decsz and of ret jmp @jtama5 ; *********************************************************************************************** sb $06.3 jmp @Barras ;******************************************************************************************************** ;******************************************************************************************************** Cross_hatch ; ****** ahora tengo que hacer portico delantero vertical ************************************** mov times,#2 otama call @linea_vac2 decsz times ; ; when I finish I leave losing 5 cycles decsz and of ret jmp @otama ; *********************************************************************************************** ; ****** ahora tengo que hacer sincro vertical ************************************************ vsync ; *********************************************************************************************** ; ****** ahora tengo que hacer 19 lineas de portico uperior y comienzo ************************* mov times,#21 jmp @cc cc nop nop otama2 call @linea_vac decsz times ; ; when I finish I leave losing 5 cycles decsz and of ret jmp @otama2 ; *********************************************************************************************** ; ****** ahora tengo que hacer 254 lineas de video ********************************************* mov times,#1 nop ftama20 call @crossv decsz times ; ; when I finish I leave losing 5 cycles decsz and of ret jmp @ftama20 mov times,#30 nop ftama1 call @crossh decsz times ; ; when I finish I leave losing 5 cycles decsz and of ret jmp @ftama1 mov times,#1 nop ftama2 call @crossv decsz times ; ; when I finish I leave losing 5 cycles decsz and of ret jmp @ftama2 mov times,#30 nop ftama3 call @crossh decsz times ; ; when I finish I leave losing 5 cycles decsz and of ret jmp @ftama3 mov times,#1 nop ftama4 call @crossv decsz times ; ; when I finish I leave losing 5 cycles decsz and of ret jmp @ftama4 mov times,#30 nop ftama5 call @crossh decsz times ; ; when I finish I leave losing 5 cycles decsz and of ret jmp @ftama5 mov times,#1 nop ftama6 call @crossv decsz times ; ; when I finish I leave losing 5 cycles decsz and of ret jmp @ftama6 mov times,#30 nop ftama7 call @crossh decsz times ; ; when I finish I leave losing 5 cycles decsz and of ret jmp @ftama7 mov times,#1 nop ftama8 call @crossv decsz times ; ; when I finish I leave losing 5 cycles decsz and of ret jmp @ftama8 mov times,#30 nop ftama9 call @crossh decsz times ; ; when I finish I leave losing 5 cycles decsz and of ret jmp @ftama9 mov times,#1 nop ftama10 call @crossv decsz times ; ; when I finish I leave losing 5 cycles decsz and of ret jmp @ftama10 mov times,#30 nop ftama11 call @crossh decsz times ; ; when I finish I leave losing 5 cycles decsz and of ret jmp @ftama11 mov times,#1 nop ftama12 call @crossv decsz times ; ; when I finish I leave losing 5 cycles decsz and of ret jmp @ftama12 mov times,#30 nop ftama13 call @crossh decsz times ; ; when I finish I leave losing 5 cycles decsz and of ret jmp @ftama13 mov times,#1 nop ftama14 call @crossv decsz times ; ; when I finish I leave losing 5 cycles decsz and of ret jmp @ftama14 mov times,#30 nop ftama15 call @crossh decsz times ; ; when I finish I leave losing 5 cycles decsz and of ret jmp @ftama15 mov times,#1 nop ftama16 call @crossv decsz times ; ; when I finish I leave losing 5 cycles decsz and of ret jmp @ftama16 ; *********************************************************************************************** ; ****** ahora tengo que hacer 8 lineas de parte inferior de pantalla ************************** mov times,#11 nop otama5 call @linea_vac decsz times ; ; when I finish I leave losing 5 cycles decsz and of ret jmp @otama5 ; *********************************************************************************************** snb $06.3 jmp @Cross_hatch jmp @Barras ; ; org 600 ;******************************************************************************************************** ;******************************************************************************************************** ;**** FUNCION CROSSH ************************************************************************************* ; 1400 cycles ;28 uSeg + 3.8 del sincro ; ; tambien lleva el sicro H esta. Y las barras de color ; 90 portico delantero ; 1284 de video ; 26 portico trasero ;************************************************************************************************ crossh mov counter,#15 ; 2 cycles ; delantero :clupit decsz counter ; 1 cycle ; jmp @:clupit ; 4 cycles ; jmp @:provi3 ;************************************************************************************************ ; Aca me quedan 1284 cycles para dibujar las barras 160 cycles cada una +2+2 ******************** :provi3 nop ; 1 cycle nop ; 1 cycle mov repeat,#9 :zir mov ra,#%11110111 ; 2 cycles jmp @:cirix :cirix mov ra,#%11110000 ; 2 cycles mov counter,#26 ; 2 cycles ; delantero :cir2 decsz counter ; 1 cycle ; jmp @:cir2 ; 4 cycles ; decsz repeat ; 1 cycle ; jmp @:zir ; 4 cycles ; nop ; 1 cycle nop ; 1 cycle nop ; ;************************************************************************************************ ;************************************************************************************************ mov counter,#5 ; 2 cycles ; delantero :clupi2 decsz counter ; 1 cycle ; jmp @:clupi2 ; 4 cycles ; nop ; 1 cycle nop ; 1 cycle ;************************************************************************************************ ;********** PULSO DE SINCRO H ******************************************************************* clrb rb.0 ; 1 cycle ; bajo el bit 6 ( comienza el pulso de sync ) mov counter,#38 ; 2 cycles :pupH1 decsz counter ; 1 cycle ; jmp @:pupH1 ; 4 cycles ; setb rb.0 ; 1 cycle ; subo el bit 6 ( termina el pulso de sync ) ;************************************************************************************************ ret ;******************************************************************************************************** ; ; ;******************************************************************************************************** ;**** FUNCION CROSSV ************************************************************************************* ; 1400 cycles ;28 uSeg + 3.8 del sincro ; ; tambien lleva el sicro H esta. Y las barras de color ; 90 portico delantero ; 1284 de video ; 26 portico trasero ;************************************************************************************************ crossv mov counter,#15 ; 2 cycles ; delantero :cvupit decsz counter ; 1 cycle ; jmp @:cvupit ; 4 cycles ; jmp @:provi :provi jmp @:provi2 ;************************************************************************************************ ; Aca me quedan 1284 cycles para dibujar las barras 160 cycles cada una +2+2 ******************** :provi2 mov ra,#%11110111 ; 2 cycles mov counter,#160 ; 2 cycles ; delantero :cxr2 nop nop nop decsz counter ; 1 cycle ; jmp @:cxr2 ; 4 cycles ; mov ra,#%11110000 ; 2 cycles nop ; 1 cycle nop ; ;************************************************************************************************ ;************************************************************************************************ mov counter,#5 ; 2 cycles ; delantero :cvupi2 decsz counter ; 1 cycle ; jmp @:cvupi2 ; 4 cycles ; nop ; 1 cycle nop ; 1 cycle ;************************************************************************************************ ;********** PULSO DE SINCRO H ******************************************************************* clrb rb.0 ; 1 cycle ; bajo el bit 6 ( comienza el pulso de sync ) mov counter,#38 ; 2 cycles :vupH1 decsz counter ; 1 cycle ; jmp @:vupH1 ; 4 cycles ; setb rb.0 ; 1 cycle ; subo el bit 6 ( termina el pulso de sync ) ;************************************************************************************************ ret ;******************************************************************************************************** ; ; org 700 ;******************************************************************************************************** ;******************************************************************************************************** ;**** FUNCION LINEA_VAC *************************************************************************************** ; 1400 cycles ;28 uSeg + 3.8 del sincro ; ; tambien lleva el sicro H esta. ;************************************************************************************************ linea_vac mov counter,#174 ; 2 cycles ; iba 173 pero con 174 anda mejor (revisar) :dlupL4 nop ; 1 cycle nop ; 1 cycle nop ; 1 cycle decsz counter ; 1 cycle ; jmp @:dlupL4 ; 4 cycles ; nop ; 1 cycle nop ; 1 cycle nop ; 1 cycle nop ; 1 cycle nop ; 1 cycle ; nop ; 1 cycle ;************************************************************************************************ ;********** PULSO DE SINCRO H ******************************************************************* clrb rb.0 ; 1 cycle ; bajo el bit 6 ( comienza el pulso de sync ) mov counter,#38 ; 2 cycles :pupH1 decsz counter ; 1 cycle ; jmp @:pupH1 ; 4 cycles ; setb rb.0 ; 1 cycle ; subo el bit 6 ( termina el pulso de sync ) ;************************************************************************************************ ret ;******************************************************************************************************** ; ; ;**** FUNCION LINEA_VAC2 *************************************************************************************** ; 1400 cycles ;28 uSeg + 3.8 del sincro ; ; volver de la ultima sub de linea_vac ( es decir esta se usa para hacer el jmp al main ) ; tambien lleva el sicro H esta. ;************************************************************************************************ linea_vac2 mov counter,#174 ; 2 cycles :dlupv4 nop ; 1 cycle nop ; 1 cycle nop ; 1 cycle decsz counter ; 1 cycle ; jmp @:dlupv4 ; 4 cycles ; nop ; 1 cycle ;************************************************************************************************ ;********** PULSO DE SINCRO H ******************************************************************* clrb rb.0 ; 1 cycle ; bajo el bit 6 ( comienza el pulso de sync ) mov counter,#38 ; 2 cycles :pupvH1 decsz counter ; 1 cycle ; jmp @:pupvH1 ; 4 cycles ; setb rb.0 ; 1 cycle ; subo el bit 6 ( termina el pulso de sync ) ;************************************************************************************************ ret ;******************************************************************************************************** ; ; ;**** FUNCION LINEA ************************************************************************************* ; 1400 cycles ;28 uSeg + 3.8 del sincro ; ; tambien lleva el sicro H esta. Y las barras de color ; 90 portico delantero ; 1284 de video ; 26 portico trasero ;************************************************************************************************ linea mov counter,#15 ; 2 cycles ; delantero :lupit decsz counter ; 1 cycle ; jmp @:lupit ; 4 cycles ; nop ; 1 cycle ; nop ; 1 cycle nop ; 1 cycle nop ; 1 cycle ;************************************************************************************************ ; Aca me quedan 1284 cycles para dibujar las barras 160 cycles cada una +2+2 ******************** nop ; 1 cycle nop ; 1 cycle ; ** BARRA ***************************************************************** mov ra,#%11110000 ; 2 cycles mov counter,#31 ; 2 cycles ; delantero jmp @:bar1 ; 4 cycles :bar1 decsz counter ; 1 cycle ; jmp @:bar1 ; 4 cycles ; ; ** BARRA ***************************************************************** mov ra,#%11110001 ; 2 cycles mov counter,#31 ; 2 cycles ; delantero jmp @:bar2 ; 4 cycles :bar2 decsz counter ; 1 cycle ; jmp @:bar2 ; 4 cycles ; ; ** BARRA ***************************************************************** mov ra,#%11110010 ; 2 cycles mov counter,#31 ; 2 cycles ; delantero jmp @:bar3 ; 4 cycles :bar3 decsz counter ; 1 cycle ; jmp @:bar3 ; 4 cycles ; ; ** BARRA ***************************************************************** mov ra,#%11110011 ; 2 cycles mov counter,#31 ; 2 cycles ; delantero jmp @:bar4 ; 4 cycles :bar4 decsz counter ; 1 cycle ; jmp @:bar4 ; 4 cycles ; ; ** BARRA ***************************************************************** mov ra,#%11110100 ; 2 cycles mov counter,#31 ; 2 cycles ; delantero jmp @:bar5 ; 4 cycles :bar5 decsz counter ; 1 cycle ; jmp @:bar5 ; 4 cycles ; ; ** BARRA ***************************************************************** mov ra,#%11110101 ; 2 cycles mov counter,#31 ; 2 cycles ; delantero jmp @:bar6 ; 4 cycles :bar6 decsz counter ; 1 cycle ; jmp @:bar6 ; 4 cycles ; ; ** BARRA ***************************************************************** mov ra,#%11110110 ; 2 cycles mov counter,#31 ; 2 cycles ; delantero jmp @:bar7 ; 4 cycles :bar7 decsz counter ; 1 cycle ; jmp @:bar7 ; 4 cycles ; ; ** BARRA ***************************************************************** mov ra,#%11110111 ; 2 cycles mov counter,#31 ; 2 cycles ; delantero jmp @:bar8 ; 4 cycles :bar8 decsz counter ; 1 cycle ; jmp @:bar8 ; 4 cycles ; mov ra,#%11110000 ; 2 cycles ;************************************************************************************************ ;************************************************************************************************ mov counter,#5 ; 2 cycles ; delantero :lupi2 decsz counter ; 1 cycle ; jmp @:lupi2 ; 4 cycles ; nop ; 1 cycle nop ; 1 cycle ;************************************************************************************************ ;********** PULSO DE SINCRO H ******************************************************************* clrb rb.0 ; 1 cycle ; bajo el bit 6 ( comienza el pulso de sync ) mov counter,#38 ; 2 cycles :pupH1 decsz counter ; 1 cycle ; jmp @:pupH1 ; 4 cycles ; setb rb.0 ; 1 cycle ; subo el bit 6 ( termina el pulso de sync ) ;************************************************************************************************ ret ;******************************************************************************************************** ;********************************************************************************************************

| file: /Techref/new/letter/news0401.htm, 32KB, , updated: 2007/7/31 16:45, local time: 2025/10/20 02:07,

216.73.216.53,10-2-207-162:LOG IN

|

| ©2025 These pages are served without commercial sponsorship. (No popup ads, etc...).Bandwidth abuse increases hosting cost forcing sponsorship or shutdown. This server aggressively defends against automated copying for any reason including offline viewing, duplication, etc... Please respect this requirement and DO NOT RIP THIS SITE. Questions? <A HREF="http://techref.massmind.org/techref/new/letter/news0401.htm"> MassMind newsletter - Video and VGA</A> |

| Did you find what you needed? |

Welcome to massmind.org! |

Welcome to techref.massmind.org! |

.