# **Extended Capabilities Port: Specifications**

Revision 1.06 July 14, 1993

# Cover Letter

**Important Note** This may not be the first time you have received the ECP Specifications. From time to time, Microsoft may make some modifications to the documentation and/or software and we want to ensure that you have the latest update to the materials. If this is not the first time you have received this kit, please read the section titled "Corrections to Previous Versions (Revisions)" very carefully for any changes that may apply to you.

Environments such as the Microsoft® Windows<sup>™</sup> operating system are making it easier for anybody to use computers, and the decision to buy computers, peripherals, and software is easier to make now that Windows provides ease of use to the personal computer (PC) environment.

Communications with peripherals is the "Achilles heel" of the industry. Low bandwidth and lack of bidirectionality have prevented suppliers of peripherals such as printers, scanners, fax/modem cards, and network adapters from introducing innovative solutions. The serial port provides bidirectionality but does not offer enough bandwidth. The standard parallel port (Centronics®) offers a higher but limited bandwidth and no bidirectionality. Centronics also requires a lot of assistance from the CPU, making it inadequate for environments such as Windows in which multiple applications are running concurrently.

The extended capabilities port (ECP) is the answer to peripheral communications problems in the PC environment. It is a fast, bidirectional parallel interface that is backwards-compatible with the existing PC standard parallel port configuration—and it uses the existing parallel connectors and cables. ECP has been jointly developed by Microsoft and Hewlett-Packard with the hopes of making it a widely adopted standard. Several chip vendors are working on designing support for ECP into their next generation I/O chips. On the system software side, Microsoft is building support for the full capabilities of ECP (bidirectionality, enhanced bandwidth, enhanced protocols) into the next generation of its Windows operating environments. A new set of application programming interfaces (APIs) will soon be available to independent software and hardware vendors (ISVs and IHVs) to enable the writing of device drivers and applications programs that take advantage of ECP.

Enclosed you will find the ECP Specification, which includes the following documents:

- ECP cover letter (this document).

- Extended Capabilities Port Protocol and ISA Interface Standard. Covers the ECP signal protocols, IEEE P1284 issues, and the ISA implementation specifications. Includes an errata sheet.

- ECP Driver Hardware Notes. Covers issues software/hardware designers must be aware of.

- ECP Compliance Test Functional Specification. Describes the setup and use of the ECP compliance test.

The ECP Specifications document describes in detail the ECP ISA implementation requirements, so you do not actually need the ECP Adaptation Kit to develop an ECP ASIC or to make ECP part of a larger chip solution. We feel, however, that having it may shorten the time required for your ECP implementation cycle.

For additional information, please contact Doug Hogarth at 206/936-3002. Doug is a Technical Evangelist in the Windows Developer Relations Group. If you are signing a contract, please send it back to:

**Doug Hogarth**

Microsoft Corporation One Microsoft Way Redmond, WA 98052

Implementing ECP accrues many obvious and substantial benefits to users. Microsoft is very excited about what we feel is the most significant event in PC/peripheral communications since the introduction of the PC, and we hope to have your support and cooperation in making this a public standard for the benefit of PC users everywhere.

Regards,

Microsoft Corporation Windows Developer Relations

# Extended Capabilities Port Protocol and ISA Interface Standard

Revision: 1.14 July 14, 1993

# **Document History**

| Revisio | on Date  | Action                                                                                                                                                                                                                                                                     | Author(s)        |

|---------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 0.1     | 5-8-92   | Described standard ISA interface for ECP ("Zippy").                                                                                                                                                                                                                        | Dave Voth (MS)   |

| 0.2     | 5-18-92  | Wrote HP's "High Speed Parallel Port Spec<br>(Zippy)" as an addendum to the BOISE / IEEE<br>P1284 specs.                                                                                                                                                                   | Rich Taylor (HP) |

| 0.3     | 7-23-92  | Edited and formatted.                                                                                                                                                                                                                                                      | Frank Williams   |

| 0.4     | 9-11-92  | Edited and formatted.                                                                                                                                                                                                                                                      | Ray Styles       |

| 0.5     | 9-18-92  | Incorporated several changes.                                                                                                                                                                                                                                              | Ray Styles       |

| 1.0     | 10-13-92 | Finalized the specification.                                                                                                                                                                                                                                               | Ray Styles       |

| 1.01    | 10-26-92 | Corrected mode switching section and switched to ECP from High Speed.                                                                                                                                                                                                      | Joseph Mouhanna  |

| 1.01    | 10-26-92 | Did same High Speed-to-ECP changes for Figures 2 and 3.                                                                                                                                                                                                                    | Ray Styles       |

| 1.02    | 11-03-92 | Modified timing for IEEE, removed fast bit and<br>added compress bit in its place.                                                                                                                                                                                         | Dave Voth        |

| 1.03    | 11-05-92 | New timing diagrams.                                                                                                                                                                                                                                                       | Joseph Mouhanna  |

| 1.04    | 11-06-92 | Minor changes.                                                                                                                                                                                                                                                             | Dave Voth        |

| 1.05    | 11-09-92 | Minor changes.                                                                                                                                                                                                                                                             | Joseph Mouhanna  |

| 1.06    | 11-12-92 | Minor changes for IEEE.                                                                                                                                                                                                                                                    | David Voth       |

| 1.07    | 12-2-92  | Minor changes.                                                                                                                                                                                                                                                             | Joseph Mouhanna  |

| 1.08    | 12-18-92 | Minor bug fixes (affects pages 16, 19, and 33 of rev 1.07).                                                                                                                                                                                                                | Joseph Mouhanna  |

| 1.09    | 01-07-93 | Minor fixes (affects pages 28 and 32 of rev 1.07 and 1.08).                                                                                                                                                                                                                | Joseph Mouhanna  |

| 1.10    | 02-04-93 | Fixes to Protocol Description (in section 2),<br>paragraphs for Reverse to Forward Phase (page<br>19) and Valid Termination (Page 20). Fixed ECP ID<br>in Figure 2 (ECP mode timing 1 of 2, page 21).<br>Fixed Table 8, page 28 (ecpAFifo and cFifo).<br>Added Appendix A. | Joseph Mouhanna  |

| 1.11    | 02-10-93 | Minor fixes to page 23 (figure 2, events 0 and 34).                                                                                                                                                                                                                        | Joseph Mouhanna  |

|         |          |                                                                                                                                                                                                                                                                            |                  |

| 1.12 | 4-28-93 | Fixed forward/reverse wording (pg. 11), P1284<br>termination (pg. 20). Minor fixes to busy signal<br>definition (pg. 26). Fixed error in compress bit in<br>cnfgB (pg. 31); added Appendix B.                                                                                                                                                                                                                                                                                                                                                                         | David Voth |

|------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 1.13 | 6-05-93 | Added bit to cnfgA (page 31), <b>ackIntEn</b> (page 35).<br>Fixed ISA Level interrupt design in Appendix B.                                                                                                                                                                                                                                                                                                                                                                                                                                                           | David Voth |

| 1.14 | 7-14-93 | nPeriphRequest (nFault), page 10;<br>nReverseRequest (nInit), page 11; Table 5 (Signal<br>Timing), page 14; Operating Phases Diagram, page<br>15; Aborting the Forward Data Transfer Phase,<br>page 19;Forward to Reverse Phase; page 19;<br>Reverse Data Transfer Phase, page 19; Timing<br>Diagrams on pages 22, 23, and 24 (new diagram on<br>page 24); Event 26 on page 25; Events 40, 48, 72,<br>73, 74, 75 on page 26; Table 7: dRq, page 29;<br>Table 11, page 31; cFIFO, page 32; Table 12, page<br>33; Table 14, page 36; DMA, page 39; added<br>Appendix C. | David Voth |

# Section 1: Introduction

#### **Document Purpose**

Design specifications from both Microsoft and Hewlett-Packard have been combined in this document to describe both the extended capabilities port (ECP) protocol, and an industry standard architecture (ISA) implementation.

#### **Other Documents**

The reader should be familiar with the *Standard P1284* by IEEE, a parent document of this document.

#### Scope

This document defines an ISA standard for the implementation of all ECP parallel port ISA devices. ECP is a joint Hewlett-Packard/Microsoft design and development effort. ECP is an enhancement to the high-speed IEEE P1284 and "BOISE" parallel port specifications.

#### Vocabulary

The following terms are used in this document:

#### assert

When a signal asserts, it transitions to a "true" state. When a signal deasserts, it transitions to a "false" state.

#### forward

Host-to-Peripheral communication.

#### reverse

Peripheral-to-Host communication.

#### PWord

A port word, equal in size to the width of the ISA interface. Typically, this can be 8 or 16 bits.

1

A high level.

#### Section 2: Signal Protocol (C) 1992-1995 Microsoft Corporation. All rights reserved.

#### 0

A low level. Each row in the following table consists of terms that are equivalent.

| PeriphClk       | nAck      |           |

|-----------------|-----------|-----------|

| HostAck         | nAutoFd   |           |

| PeriphAck       | Busy      |           |

| nPeriphRequest  | nFault    |           |

| nReverseRequest | nInit     |           |

| nAckReverse     | PError    |           |

| Xflag           | Select    |           |

| ECPmode         | BOISEmode | nSelectIn |

| HostClk         | nStrobe   |           |

# Section 2: Signal Protocol

### Overview

This section describes a high-performance, bidirectional signal protocol that was jointly developed by Hewlett-Packard and Microsoft. Only the protocol is described in this section; for information related to the standard PC ISA hardware implementation of the protocol, refer to Section 3.

This specification is an enhancement to the IEEE P1284 standard, which describes three basic data transfer modes:

- Compatible mode (forward channel, industry-standard parallel port interface)

- Nibble mode (reverse channel, compatible with all existing PC hosts)

- Byte mode (reverse channel, compatible with IBM® PS/2® hosts)

This document describes two very similar additional modes that may be nested within the P1284 standard:

- ECP mode (fast bidirectional; requires custom hardware on interfaces)

- ECP mode including RLE decompression

The ECP modes conform to the conventions and philosophies established in the IEEE P1284 standard and will be implemented on future generations of hosts and peripherals. To attain the highest performance, hardware is required on both the peripheral and host. ECP boosts the I/O bandwidth to meet the demands of high-performance peripherals.

Hewlett-Packard and Microsoft recommend that the ECP modes be incorporated into the IEEE P1284 standard. Hewlett-Packard and Microsoft are taking steps to ensure that the ECP becomes a de facto standard throughout the personal computer industry.

ECP provides a number of advantages, some of which are listed below. The individual features are explained in greater detail in the remainder of the document.

- High-performance half-duplex forward and reverse channel

- Interlocked handshake, for fast, reliable transfer

- Optional single-byte RLE compression for improved throughput (64:1)

- Channel addressing for low-cost peripherals

- Link and data layer separation

- Use of active output drivers

- Use of adaptive signal timing

- Peer-to-peer capability

# Description

#### Supplementary signal definitions

The ECP modes conform to the signal line definitions established by the proposed IEEE 1284 specification (also termed "BOISE"). However, a few signal lines have alternate uses during ECP mode.

The following signals are redefined to provide additional functionality in ECP mode.

# Compatible mode Nibble/Byte mode

| Compatible mode |           | Nibble/Byle mode |                 |

|-----------------|-----------|------------------|-----------------|

| nFault          |           | nDataAvailable   | nPeriphRequest  |

|                 | nSelectIn | RnW              | BOISEmode       |

|                 | nInit     | always high      | nReverseRequest |

|                 | PError    | AckDataReq       | nAckReverse     |

|                 | nAutoFd   | HostBusy         | HostAck         |

|                 | Busy      | PeriphBusy       | PeriphAck       |

|                 |           |                  |                 |

FCP mode

#### nPeriphRequest (nFault)

During ECP mode the peripheral is permitted (but not required) to drive this pin low to request a reverse transfer. The request is merely a "hint" to the host; the host has ultimate control over the transfer direction. This signal provides a mechanism for peer-to-peer communication. This signal typically would be used to generate an interrupt to the host CPU. The signal is asserted low and kept there until the interrupt is serviced or the port exits ECP mode.

#### **BOISEmode (nSelectin)**

This pin is driven high during all P1284 modes. It is driven low to terminate. This signal operates the same in ECP mode as in Nibble/Byte mode, but the name has been changed because "RnW" was inappropriate for a bidirectional mode.

#### nReverseRequest (nInit)

This pin is driven low to place the channel in the reverse direction. The peripheral is only allowed to drive the bidirectional data bus while in ECP mode, when BOISEmode is high and nReverseRequest is low.

#### nAckReverse (PError)

The peripheral drives this signal low to acknowledge nReverseRequest. It is an "interlocked" handshake with nReverseRequest. The host relies upon nAckReverse to determine when it is permitted to drive the data bus.

#### HostAck (nAutoFd)

The host drives this signal to flow control in the reverse direction. It is an "interlocked" handshake with nAck. HostAck also provides command information in the forward phase.

#### PeriphAck (Busy)

The peripheral uses this signal to flow control in the forward direction. It is an "interlocked" handshake with nStrobe. PeriphAck also provides command information in the reverse direction.

#### **Negotiation into ECP modes**

Negotiation into the ECP modes from Compatibility mode is accomplished according to the established P1284 methodology, with a few minor differences. The following P1284 extensibility request values are provided for ECP:

#### **Table 2. Extensibility Request Values**

| Extensibility Request Value | Definition                         |

|-----------------------------|------------------------------------|

| 0001 0000                   | ECP mode                           |

| 0001 0100                   | ECP Device ID                      |

| 0011 0000                   | ECP mode with RLE compression      |

| 0011 0100                   | ECP Device ID with RLE compression |

| 0010 0000                   | Reserved                           |

| 0010 0100                   | Reserved                           |

During negotiation, Xflag (Select) is driven high to indicate that the peripheral supports the request transfer mode. Unlike Nibble/Byte modes, the nDataAvail (nFault) does *not* indicate the availability of data during negotiation (or thereafter). Also, nDataAvail (nFault) is redefined as nPeriphRequest during ECP mode.

Immediately following negotiation (and a short setup phase), the interface defaults to the forward direction. If no forward channel data is to be transmitted, the interface may then be reversed.

### **Termination from ECP mode**

Termination from ECP mode is similar to the termination from Nibble/Byte modes. The host is permitted to terminate from ECP mode only in specific, well-defined states. The termination can only be executed while the bus is in the forward direction. To terminate while the channel is in the reverse direction, it must first be transitioned into the forward direction.

#### **Device ID**

Device ID for High Speed devices is handled in the conventional manner as defined in the proposed IEEE 1284 specification. That is, when the Device ID Request and ECP Mode Request bits are both asserted in the Extensibility Request Value during negotiation, the High Speed device will return the standard P1284 Device ID string. Channel Addressing is not used during Device ID. Compression may optionally be used during Device ID. Forward channel data is not sent during Device ID mode. To transfer normal data, the host must first terminate from the Device ID mode and renegotiate with the Device ID Request bit deasserted in the Extensibility Request Value.

#### Command/Data

ECP mode supports two advanced features to improve the effectiveness of the protocol for some applications. The features are implemented by allowing the transfer of normal 8-bit data or 8-bit commands.

When in the forward direction, normal data is transferred when (HostAck) nAutoFd is high and an 8-bit command is transferred when (HostAck) nAutoFd is low. The most significant bit of the command indicates whether it is a run-length count (for compression) or a channel address.

Table 3. Forward Channel Commands (When HostAck Is Low)

| D7 | D[6:0]                                         |

|----|------------------------------------------------|

| 0  | Run-Length Count (0-127) (mode 0011 0X00 only) |

| 1  | Channel Address (0-127)                        |

|    |                                                |

When in the reverse direction, normal data is transferred when busy (PeriphAck) is high and an 8-bit command is transferred when busy (PeriphAck) is low. The most significant bit of the command is always zero. Reverse channel addresses are seldom used and may not be supported in hardware.

| <b>Table 4. Reverse Channel Commands</b> | (When PeriphAck Is Low) |

|------------------------------------------|-------------------------|

|------------------------------------------|-------------------------|

| D7     | D[6:0]                                              |                       |

|--------|-----------------------------------------------------|-----------------------|

| 0<br>1 | Run-Length Count (0-127)<br>Channel Address (0-127) | (mode 0011 0X00 only) |

#### Optional support of compression/decompression

Devices may or may not choose to support decompression via the negotiation sequence. Devices that negotiate into ECP RLE mode (mode 0011 0X00) must support decompression of RLE data and may optionally compress it. Devices using the non-RLE ECP mode *must not* transfer compressed data.

#### **Data Compression**

To provide the potential for increased performance, a simple data compression (64:1max, 4:1 typical) technique is built into the protocol specification. Single-byte, run-length encoding is supported, which compresses strings of identical bytes while guaranteeing that incompressible data will not be expanded. The compression is particularly useful on raster imaging devices. The decompression/compression is handled very simply and economically in hardware. This simple compression does not preclude the use of other data compression schemes at a higher (data stream or packet) level.

When a run-length count is received, the subsequent data byte is replicated the specified number of times. A run-length count of zero specifies that only one byte of data is represented by the next data byte, whereas a run-length count of 127 indicates that the next byte should be expanded to 128 bytes. To prevent data expansion, however, run-length counts of zero should be avoided.

#### **Channel Addressing**

To support simple, low-cost peripherals that do not desire to parse a data stream or packet, a channel-addressing scheme is provided in ECP mode. ECP mode provides 128 channel addresses. The channel addresses may be dynamically changed while in ECP mode. The support of channel addresses does not incur any overhead for typical devices that wish to transmit or receive only data stream or packet data (stream or packet peripherals may ignore channel addresses). Specific channel address definitions are device-specific. Although the use of channel addresses seemingly violates the P1284 specification's data and link layer separation philosophy, it is permissible because the use of addresses is optional for the peripheral. The channel address defaults to zero after each negotiation. After a channel address command is issued, the address remains in effect indefinitely until another channel address command is issued, or until termination.

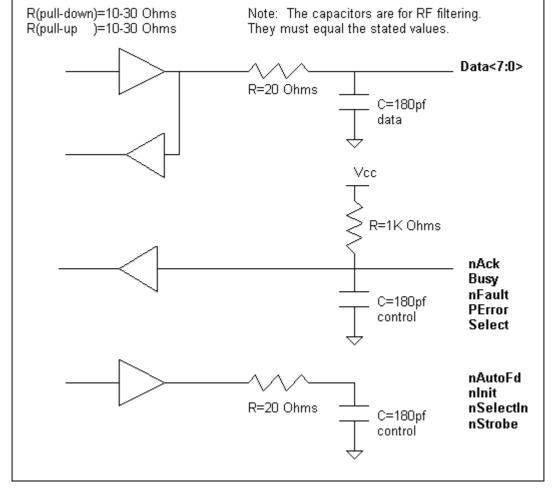

#### **Output Drivers**

To facilitate higher performance data transfer, the use of balanced CMOS active drivers for critical signals (Data, HostAck, HostClk, PeriphAck, PeriphClk) is permitted and encouraged during ECP mode. Because the use of active drivers can present compatibility problems in Compatible mode (the control signals, by tradition, are specified as open-collector), the drivers may be dynamically changed from open-collector to totem-pole. The timing for the dynamic driver change is specified in this document. The dynamic driver change must be implemented properly to prevent glitching the outputs.

#### **Signal Timing**

The signal timing for ECP mode is designed for performance and reliability over cabled systems.

| Time           | Minimum                                                                         | Maximum  |

|----------------|---------------------------------------------------------------------------------|----------|

| T <sup>⊢</sup> | 0                                                                               | 1.0 sec. |

| T <sup>⊤</sup> | 0                                                                               | infinite |

| T∟             | 0                                                                               | 35 ms    |

| T <sup>s</sup> | 35ms                                                                            |          |

| Τ <sup>Ρ</sup> | 500 ns                                                                          |          |

| TD             | 0 ns                                                                            |          |

| TR             | Host may enter Data Transfer Recovery after TS (Software application dependent) |          |

|                |                                                                                 |          |

# Table 5. Signal Timing

The use of interlocked handshaking provides reliable data transfers. Interlocked handshaking

also provides the ability to make trade-offs concerning performance and reliability at the host or peripheral (analog or digital filtering may be implemented to improve noise immunity or support long cables, at the cost of reduced performance).

The timing is completely self-adapting, allowing more time for systems using longer cables.

#### **Peer-to-Peer Capability**

Unlike other P1284 modes, the ECP mode may reverse the channel direction at will without having to renegotiate. In addition, a rudimentary "peer-to-peer" capability is provided that allows the peripheral to indicate to the host when it would like to reverse the channel (the host is always in ultimate control of the channel direction, however).

### Operation

#### **Operating Phases**

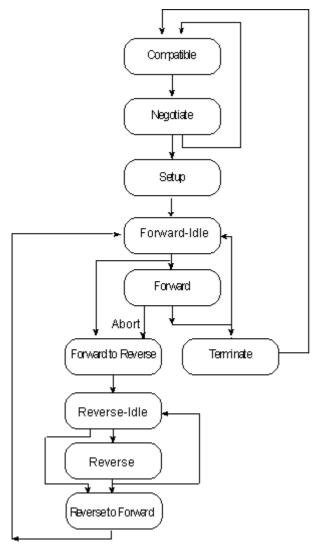

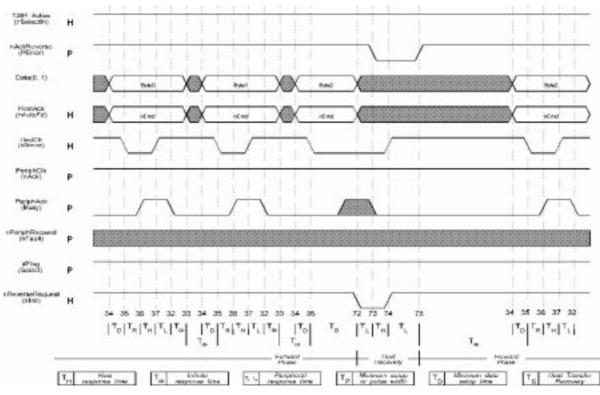

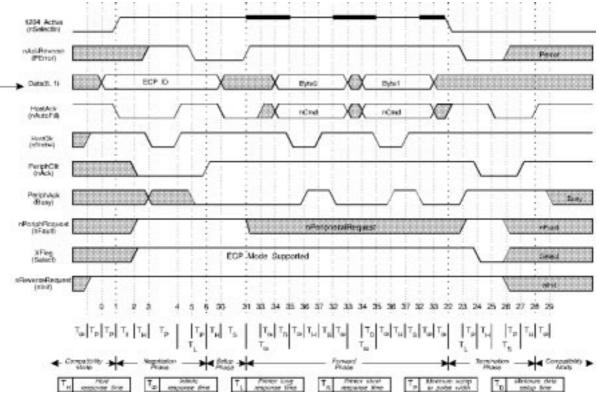

#### Figure 1. Phase transition diagram

The P1284 interface operates in phases. Additional phases are defined for use in the ECP mode as described below. These phases represent the state of the interface as data is moved between the host and the printer. The transitions are based on the present state of the interface, signal transitions from the host and the printer, and time-outs.

#### **Compatible Data Transfer phase**

Interface is in compatible mode, performing host-to-printer data transfer.

#### **Compatible Idle phase**

Interface is in compatible mode, no data transfer. Printer status lines indicate current parallel port status.

#### **Reverse Data Transfer phase**

Interface is in ECP mode, performing printer-to-host data transfer.

#### **Negotiation phase**

Signal handshaking to change interface from compatible mode to P1284 mode.

#### Setup phase

This phase immediately follows the Negotiation phase (it is actually part of the negotiation, but it differs from Nibble/Byte modes, so it is denoted separately) and is necessary to set up the interface signals to the correct state for the Forward Data Transfer phase. The interface may optionally switch from open-collector to active-drive outputs during this phase.

#### Forward-Idle

When the host has no data to send, it keeps HostClk (nStrobe) high and the peripheral will leave PeriphAck (Busy) low.

#### Forward Data Transfer phase

The interface transfers data and commands from the host to the peripheral using an interlocked PeriphAck and HostClk. The peripheral may indicate its desire to send data to the host by asserting nPeriphRequest.

#### Forward to Reverse phase

The interface is changing from the forward direction to the reverse direction.

#### **Reverse-Idle phase**

The peripheral has no data to send and keeps PeriphClk high. The host is idle and keeps HostAck low.

#### **Reverse Data Transfer phase**

The interface transfers data and commands from the peripheral to the host using an interlocked HostAck and PeriphClk.

#### **Reverse to Forward phase**

The interface is changing from the reverse direction to the forward direction.

#### **Termination phase**

Signal handshaking to change from P1284 mode to Compatible mode. Also, the output drivers return to open-collector in this phase. Termination may only be accomplished from the Forward Data Transfer phase.

#### **ECP Mode Interface Errors**

Errors can occur during interface transfers due to time-outs, noise, incorrect protocol implementation, device being powered off, and so on. Many errors can be detected by both the host computer and the printer. When the host or peripheral detects an error, it should immediately abort (with no termination phase) and resume Compatibility mode operation.

In particular, to protect against bus fight conditions on the bidirectional data pins, the peripheral must immediately (within  $1\mu$ S) stop driving the data bus in the event of a protocol exception.

The peripheral should carefully monitor both BOISEmode (nSelectIn) and nReverseRequest (nInit) to detect when the host has aborted to Compatibility mode.

When a High Speed device detects an error, it should terminate the current transfer and assume that the current byte was not successfully transferred. The interface provides no error detection on the data itself. Any desired error detection and recovery should be handled at a higher level.

# **Protocol Description**

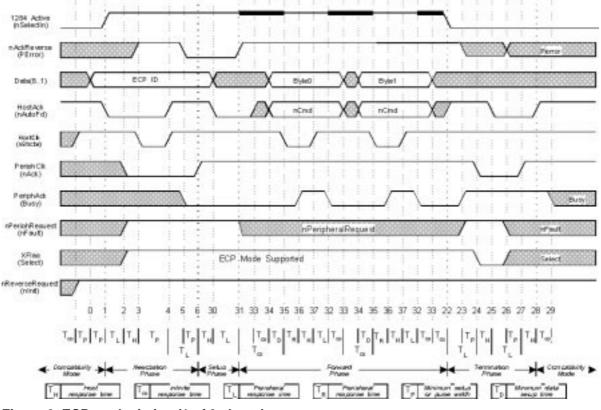

The High Speed protocol is described in the following section. Timing diagrams are provided to detail the handshake sequences. Along the bottom of each diagram are numbers corresponding to signal transition events. These events are listed in the "Event List" section. The event numbers are also shown in parentheses in the textual descriptions below to improve readability of the diagrams.

### **High Speed Negotiation Phase**

To begin the Negotiation phase, the host places the High Speed extensibility request value on the data bus (event 0), then sets BOISEmode (nSelectIn) high and HostAck (nAutoFd) low (event 1). The peripheral responds by setting PeriphClk (nAck) low, nPeriphRequest (nFault) high, Xflag(Select) high, and nAckReverse (PError) high (event 2). The host then sets HostClk (nStrobe) low (event 3). The host then sets HostClk (nStrobe) and HostAck (nAutoFd) high (event 4), acknowledging that it has recognized a High Speed compatible peripheral. The peripheral then sets nAckReverse (PError) low, PeriphAck (Busy) low, and Xflag (Select) high if it supports ECP mode (event 5). The printer then sets PeriphClk (nAck) high (event 6), indicating that the other status lines may be read. The interface now enters the Setup phase. Figure 2 demonstrates a successful negotiation.

Figure 2. ECP mode timing (1 of 3 charts)

#### **Failed Negotiation**

If the peripheral does not support ECP mode, it will set Xflag(Select) low during negotiation.

When this occurs, the host must terminate the session and renegotiate for another transfer mode. This sequence is fully documented in the P1284 specification.

#### **Setup Phase**

The Setup phase is entered immediately following a successful negotiation. After seeing PeriphClk (nAck) go high, the host optionally changes to active drivers and sets HostAck (nAutoFd) low (event 30). The peripheral responds by setting nAckReverse (PError) high and optionally changing to active drivers (event 31). The interface now enters the Forward phase. The setup phase transitions are shown in Figure 2.

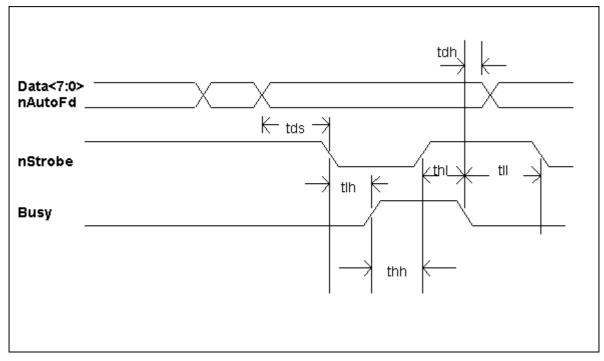

### Forward Data Transfer Phase

The Forward Phase may be entered from the Forward-Idle Phase. When the peripheral is not busy it sets PeriphAck (Busy) low (event 32). The host then sets HostClk (nStrobe) low when it is prepared to send data (event 35). The data must be stable for the specified setup time prior to the falling edge of HostClk. The peripheral then sets PeriphAck (Busy) high to acknowledge the handshake (event 36). The host then sets HostClk (nStrobe) high (event 37). The peripheral then accepts the data and sets PeriphAck (Busy) low, completing the transfer. This sequence is shown in Figure 2.

The timing is designed to provide three cable round-trip times for data setup if Data is driven simultaneously with HostClk (nStrobe).

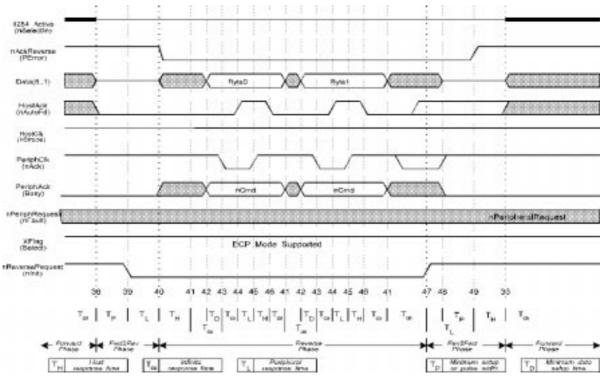

#### Aborting the Forward Data Transfer phase

There is a possibility of the forward channel becoming stalled. The stall condition will exist if the peripheral is unable to accept the data byte being transferred by the host at event 35. In this condition the peripheral will not acknowledge the handshake (event 36). A mechanism has been provided to recover from this condition. If the host, following event 35, determines that a stall condition may exist, the host may abort the transfer of the current byte by setting nReverseRequest (nInit) low (event 72). The peripheral, regardless of whether it has accepted the byte from the host (event 36 happened), shall discard the byte (if applicable) and acknowledge the host by setting nAckReverse (PError) low. The host then returns nReverseRequest (nInit) high (event 74) and the peripheral follows by returning nAckReverse (PError) high (event 75). This sequence, shown in Figure 4, will return the interface to the state that existed prior to host event 35.

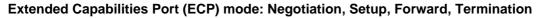

#### Forward to Reverse Phase

The Forward to Reverse phase is entered from the Forward phase. The host tri-states the data bus and sets HostAck (nAutoFd) low (event 38). After waiting for the minimum setup time, the host then sets nReverseRequest (nInit) low (event 39). The peripheral then acknowledges the reversal by setting nAckReverse (PError) low (event 40). The peripheral is now permitted to drive the data bus after setting nStrobe high. The interface now enters the Reverse phase. This sequence is shown in Figure 3.

# Extended Capabilities Port (ECP) Mode: Forward to Reverse (Fwd2Rev), Reverse, Reverse to Forward (Rev2Fwd)

#### Section 2: Signal Protocol (C) 1992-1995 Microsoft Corporation. All rights reserved.

Figure 3. ECP mode timing (2 of 3)

#### Extended Capabilities Port (ECP) Mode: Host Transfer Recovery

# Figure 4. ECP mode timing (3 of 3)

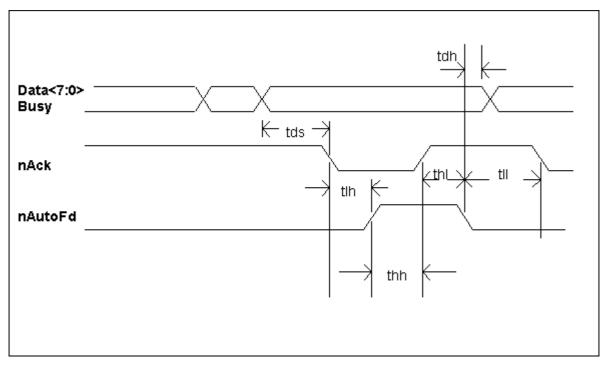

# **Reverse Data Transfer Phase**

The Reverse phase may be entered from the Reverse-Idle phase. After the previous byte has been accepted, the host sets HostAck (nAutoFd) low (event 46). The peripheral then sets

PeriphClk (nAck) low when it has data to send (event 43). The data must be stable for the specified setup time prior to the falling edge of PeriphClk. When the host is ready to accept a byte, it sets HostAck (nAutoFd) high to acknowledge the handshake (event 44). The peripheral then sets PeriphClk (nAck) high, causing the host to accept the data (event 45). After the host has accepted the data, it sets HostAck (nAutoFd) low (event 46), completing the transfer. This sequence is shown in Figure 3.

#### **Reverse to Forward Phase**

The Reverse to Forward phase is entered from the Reverse phase. HostAck (nAutoFd) may be high or low when the Reverse to Forward phase is entered. The host sets nReverseRequest (nInit) high (event 47). The peripheral then tri-states the data bus, sets PeriphAck (Busy) low to indicate the proper forward channel status, and sets PeriphClk (nAck) high (event 48). If the peripheral was in the middle of a data transfer (PeriphClk low), it assumes that the data byte will be discarded by the host and suspends the transfer. After waiting the minimum setup time, the peripheral then sets nAckReverse (PError) high to acknowledge the change of direction (event 49). The host is now permitted to drive the data bus. The interface now enters the Forward phase. This sequence is shown in Figure 3.

#### **Valid Termination**

To terminate from P1284 mode, the host sets BOISEmode (nSelectIn) low (event 22), which will initiate one of two types of termination. The first type is a handshake that allows the printer to tell the host when it has returned to compatible mode. The second is an immediate abort, with no guarantee of interface integrity. If the interface was in a "valid" state, which is any state where a reverse data transfer is not in progress, the printer will perform the handshake. If the interface was not in a "valid" state, the printer will abort immediately. Valid states are indicated in the data transfer diagrams by BOISEmode (nSelectIn) being shown as a heavy line.

To terminate from a valid state, the printer will respond to BOISEmode (nSelectIn) being set low by setting nAckReverse(PError) to low and PeriphAck (Busy) and nPeriphRequest (nFault) high (event 23). The printer will then set Xflag (Select) to its opposite sense and PeriphClk (nAck) low (event 24). The host then sets HostAck (nAutoFd) low (event 25). The printer then sets the compatible mode printer status on nPeriphRequest (nFault), Xflag (Select) and nAckReverse (PError) while the host sets the compatible mode status on nReverseRequest (nInit) (event 26). The printer then sets PeriphClk (nAck) high (event 27). The host ends the termination handshake by setting HostAck (nAutoFd) high (event 29), which returns the interface to the compatible mode idle phase. The printer may then change PeriphAck (Busy) (event 30) to accept host-to-printer data. This sequence is shown following a data transfer in Figure 2.

#### Aborting a Transfer

When BOISEmode (nSelectIn) is set low in an invalid state, the printer aborts immediately. This is to protect both the printer and the host. The unexpected transition of BOISEmode (nSelectIn) and possibly other signals could be caused by a user switching a switch box at the wrong time, or a cable that has worked loose. If a reverse channel data transfer is aborted, the current byte in transit is lost, but the printer will hold that byte in its output register. The next time the host performs a reverse channel transfer, that byte will be the first one sent.

# **Event List**

The timing charts that constitute Figures 2, 3, and 4 contain numbers corresponding to the events that cause the transitions. Following is a list of those numbers and descriptions of the corresponding events.

#### **Figure 2 Numbers and Events**

- 0 Host sets extensibility request value on data bus.

- 1 Host requests a ECP mode transfer by setting BOISEmode (nSelectIn) high and HostAck (nAutoFd) low.

- 2 Peripheral indicates ECP mode support by setting nAckReverse (PError), Xflag (Select), and nPeriphRequest (nFault) high, and PeriphClk (nAck) low.

- 3 Host sets HostClk (nStrobe) low to latch extensibility request value into printer.

- 4 After waiting the minimum HostClk (nStrobe) pulse width, the host sets HostClk (nStrobe) and HostAck (nAutoFd) high to acknowledge the peripheral's support of the High Speed protocol.

- 5 Peripheral sets nAckReverse (PError) low. Xflag (Select) is set to reflect the peripheral's support of the requested extension. PeriphAck (Busy) is set to indicate whether the printer can accept data from the host.

- 6 Peripheral sets PeriphClk (nAck) high, informing the host that the four interface status signals are valid.

**Note:** Events 7 through 21 are defined in the IEEE P1284 specification document; these events deal with Byte and Nibble modes and are not discussed here.

- 22 Host sets BOISEmode (nSelectIn) low and HostAck (nAutoFd) high to request termination of ECP mode.

- 23 Peripheral sets PeriphAck (Busy) and nPeriphRequest (nFault) high, and nAckReverse (PError) low.

- 24 Peripheral acknowledges host's request by setting PeriphClk (nAck) low and Xflag (Select) to its opposite sense.

- 25 Host handshakes with peripheral by setting HostAck (nAutoFd) low.

- 26 Peripheral sets nAckReverse (PError), nPeriphRequest (nFault), and Xflag (Select) to their current compatible mode values. PeriphAck (Busy) is still high to block incoming data.

- 27 Peripheral completes handshake by setting PeriphClk (nAck) high.

- 28 Host completes handshake by setting HostAck (nAutoFd) high.

- 29 Peripheral updates PeriphAck (Busy) to current compatible mode status.

- 30 Host sets HostAck (nAutoFd) low to acknowledge successful negotiation.

- 31 Peripheral acknowledges that it is now operating in ECP mode by raising nAckReverse (PError). PeriphAck (Busy) and nPeriphRequest (nFault) are now active.

- 32 The peripheral drives HostAck (nAutoFd) low, indicating that it has accepted the data. This signals the end of the transfer.

- 33 The host is idle.

- 34 Host places Data on the bus. The command bit (nCmd/HostAck) is driven to the appropriate level.

- 35 The host sets HostClk (nStrobe) low to indicate valid data is on the bus.

- 36 The peripheral handshakes, setting PeriphAck (Busy) high.

- 37 The host raises nStrobe to continue the handshake. The peripheral will use this edge of nStrobe to latch the data.

#### Figures 3 and 4, Numbers and Events

- 38 The host tri-states the Data bus and sets HostAck (nAutoFd) low to prepare for a bus reversal.

- 39 The Host sets nReverseRequest (nInit) low to initiate a bus reversal.

- 40 The peripheral sets nAckReverse (PError) low to acknowledge the bus reversal. (nAutoFd) is now active.

- 41 The peripheral is now idle.

- 42 The peripheral drives Data and nCmd (Busy) onto the bus.

- 43 The peripheral sets PeriphClk (nAck) low to indicate that data is available on the bus.

- 44 The host acknowledges the assertion of PeriphClk (nAck) by setting HostAck (nAutoFd) high.

- 45 The peripheral continues the handshake by setting PeriphClk (nAck) high.

- 46 The host completes the transfer, accepting the byte by setting HostAck (nAutoFd) low.

- 47 The host sets nReverseRequest (nInit) high to initiate a bus reversal (back to the forward direction). The host may continue to handshake, receiving "don't care" data.

- 48 The peripheral terminates any ongoing transfer, tri-states the data bus, sets PeriphClk (nAck) high, and places valid status on the PeriphAck (Busy) line.

- 49 The peripheral acknowledges that the bus has been relinquished by setting nAckReverse

(PError) high.

- 50 The host drives the data bus and continues with forward data transfer.

- 72 After waiting for the minimum required time (Ts), the host may abort the host to peripheral transfer in progress by setting nReverseRequest (nInit) low.

- 73 The peripheral handshakes, setting nAckReverse (PError) low, and if not already PeriphAck (Busy) low, indicating that the peripheral-to-host data transfer in progress has been aborted and the data byte has been discarded.

- 74 The host raises nReverseRequest to continue the handshake.

- 75 The peripheral completes the handshake by raising nAckReverse (PError) high, returning the link to a host-idle condition.

# Section 3: ISA Implementation Standard

### Overview

This specification describes the standard ISA interface to the extended capabilities port (ECP). All ISA devices supporting ECP must meet the requirements contained in this section or the port will not be supported by Microsoft.

#### Description

The port is software- and hardware-compatible with existing parallel ports so that it may be used as a standard LPT port if ECP is not required. The port is designed to be simple and requires a small number of gates to implement. It does not do any "protocol" negotiation, rather it provides an automatic high-burst bandwidth channel that supports DMA for ECP in both the forward and reverse directions.

Small FIFOs are employed in both forward and reverse directions to smooth data flow and improve the maximum bandwidth requirement. The size of the FIFO must be at least 16 bytes deep.

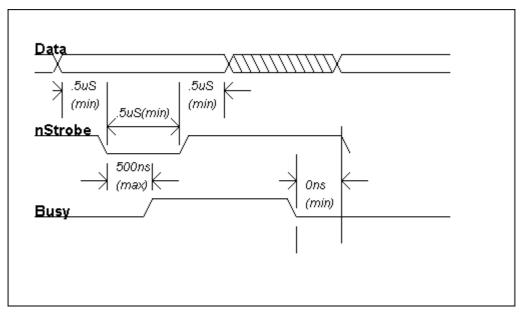

The port supports an automatic handshake for the standard parallel port to improve compatibility mode transfer speed.

The port also supports run-length encoded (RLE) decompression (required) in hardware. Compression is accomplished by counting identical bytes and transmitting an RLE byte that indicates how many times the next byte is to be repeated. Decompression simply intercepts the RLE byte and repeats the following byte the specified number of times. Hardware support for compression is optional. Please consult Section 2 for signal protocol details on ECP.

|          |     |     | J             |                |                                                                                                                                                                                                                            |

|----------|-----|-----|---------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name     | Qty | Dir | Host<br>Pin # | Slave<br>Pin # | ECP Function                                                                                                                                                                                                               |

| nStrobe  | 1   | 0   | 1             | 1              | During write operations nStrobe registers data or address into the slave on the asserting edge (handshakes with Busy).                                                                                                     |

| data<7:0 | >8  | I/O | 9-2           | 9-2            | Contains address or data or RLE data.                                                                                                                                                                                      |

| nAck     | 1   | Ι   | 10            | 10             | Indicates valid data driven by the peripheral when asserted. This signal handshakes with nAutoFd in reverse.                                                                                                               |

| Busy     | 1   | I   | 11            | 11             | This signal deasserts to indicate that the periphera<br>can accept data. This signal handshakes with<br>nStrobe in the forward direction. In the reverse<br>direction this signal, when low, indicates the data is<br>RLE. |

# Description of Pins

#### Table 6. ECP Parallel Port Signal List

| PError    | 1   | I | 12 | 12             | Used to acknowledge a change in the direction the transfer (asserted = forward).                                                                                                                                       |

|-----------|-----|---|----|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Select    | 1   | I | 13 | 13             | Indicates printer on line.                                                                                                                                                                                             |

| nAutoFd   | 1   | 0 | 14 | 14             | Requests a byte of data from the peripheral when<br>asserted, handshaking with nAck in the reverse<br>direction. In the forward direction this signal indicates<br>whether the data lines contain ECP address or data. |

| nFault    | 1   | I | 15 | 32             | Generates an error interrupt when asserted.                                                                                                                                                                            |

| nInit     | 1   | 0 | 16 | 31             | Sets the transfer direction (asserted = reverse, deasserted = forward).                                                                                                                                                |

| nSelectIr | า 1 | 0 | 17 | 36             | Always deasserted in ECP mode.                                                                                                                                                                                         |

| gnd       | 1   | — | 18 | 33             | Aux-Out                                                                                                                                                                                                                |

| gnd       | 1   | — | 19 | 19             | Return ground for strobe.                                                                                                                                                                                              |

| gnd       | 1   | — | 20 | 21             | Return ground for data<1>.                                                                                                                                                                                             |

| gnd       | 1   | — | 21 | 23             | Return ground for data<3>.                                                                                                                                                                                             |

| gnd       | 1   | — | 22 | 25             | Return ground for data<5>.                                                                                                                                                                                             |

| gnd       | 1   | — | 23 | 27             | Return ground for data<7>.                                                                                                                                                                                             |

| gnd       | 1   | — | 24 | 29             | Return ground for Busy.                                                                                                                                                                                                |

| gnd       | 1   | — | 25 | 30             | Return logic ground.                                                                                                                                                                                                   |

| gnd       |     |   | NC | 20             | Grounded on Connector.                                                                                                                                                                                                 |

| gnd       |     |   | NC | 22             | Grounded on Connector.                                                                                                                                                                                                 |

| gnd       |     |   | NC | 24             | Grounded on Connector.                                                                                                                                                                                                 |

| gnd       |     |   | NC | 26             | Grounded on Connector.                                                                                                                                                                                                 |

| gnd       |     |   | NC | 28             | Grounded on Connector.                                                                                                                                                                                                 |

|           |     |   | NC | 15-17<br>34-35 | Unused.                                                                                                                                                                                                                |

#### **ISA Connections**

The interface can never stall, causing the host to hang. The width of data transfers is strictly controlled on an I/O address basis per this specification. All FIFO-DMA transfers are PWord wide, PWord aligned, and end on a PWord boundary. (The PWord value can be obtained by reading Configuration Register A, **cnfgA**, described in the next section.) Single-byte-wide transfers are always possible with standard or PS/2 mode using program control of the control signals.

| Table | 7. IS | A Inte | erface |

|-------|-------|--------|--------|

|-------|-------|--------|--------|

| Name       | Qty  | Dir | Function                                                               |

|------------|------|-----|------------------------------------------------------------------------|

| da<10:0>   | 11   | I/O | System Address bus                                                     |

| sd<15-7:0> | 16-8 | I/O | System Data Bus                                                        |

| ~ioR       | 1    | I   | I/O Read Command                                                       |

| ~ioW       | 1    | I   | I/O Write Command                                                      |

| ~ioCs16    | 1    | 0   | I/O is 16 bit                                                          |

| dRq        | 1    | 0   | DRQ DMA Request<br>(Note: Use a 1K pulldown here to prevent requests.) |

| ~dAck      | 1    | I   | DACK DMA Grant                                                         |

| iRq        | 1    | 0   | IRQ                                                                    |

| sysClk     | 1    | I   | System Clock                                                           |

| resetDrv   | 1    | I   | Reset                                                                  |

#### **Register Definitions**

The register definitions are based on the standard IBM addresses for LPT. All of the standard printer ports are supported. The additional registers attach to an upper bit decode of the standard LPT port definition to avoid conflict with standard ISA devices.

The port is equivalent to a generic parallel port interface and may be operated in that **mode**. The port registers vary depending on the **mode** field in the **ecr**. The table below lists these dependencies. Operation of the devices in modes other that those specified is undefined.

|          | gioter Den |       |       |         |                          |

|----------|------------|-------|-------|---------|--------------------------|

| Name     | Address    |       | Size  | Mode    | Function                 |

| data     | 0x000      | R/W   | byte  | 000-001 | Data Register            |

| ecpAFifo | 0x000      | W-R/W | byte  | 011     | ECP FIFO (Address)       |

| dsr      | 0x001      | R     | byte  | All     | Status Register          |

| dcr      | 0x002      | R/W   | byte  | All     | Control Register         |

| cFifo    | 0x400      | W-R/W | PWord | 010     | Parallel Port Data FIFO  |

| ecpDFifo | 0x400      | R/W   | PWord | 011     | ECP FIFO (Data)          |

| tFifo    | 0x400      | R/W   | PWord | 110     | Test FIFO                |

| cnfgA    | 0x400      | R-R/W | byte  | 111     | Configuration Register A |

| cnfgB    | 0x401      | R-R/W | byte  | 111     | Configuration Register B |

| ecr      | 0x402      | R/W   | byte  | All     | Extended Control Reg.    |

|          |            |       |       |         |                          |

Note that all addresses shown in Table 8 are added to the base of 03bch, 0278h, 0378h.

#### data

0x000 modes 000,001 (Parallel Port Data Register)

This is the standard parallel port data register. Writing to this register in mode 000 will drive data to the parallel port data lines. In all other modes the drivers may be tri-stated by setting the **direction** bit in the **dcr**. Reads to this register return the value on the data lines.

#### ecpAFifo

0x000 mode 011 (ECP FIFO: Address/RLE)

A data byte written to this address is placed in the FIFO and tagged as a ECP Address/RLE. The hardware at the ECP port will transmit this byte to the peripheral automatically. The operation of this register is defined only for the forward direction (**direction** is 0).

#### Table 9. ECP Address FIFO

Table 8. Register Definitions

| <7>   | W  | Indicates data Type                                                                                                                                                     |

|-------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 1: | Bits <6:0> are a ECP Address                                                                                                                                            |

|       | 0: | Bit field <6:0> is a run length, indicating how many times the next data byte is to appear $(0 = 1 \text{ time}, 1 = 2 \text{ times}, 2 = 3 \text{ times}, and so on).$ |

| <6:0> | W  | Address or RLE field described above.                                                                                                                                   |

|       |    |                                                                                                                                                                         |

#### dsr

0x001 (Device Status Register)

This read-only register reflects the inputs on the parallel port interface.

#### Table 10. Device Status Register

| <7>   | R | nBusy    | inverted version of parallel port <b>Busy</b> signal |

|-------|---|----------|------------------------------------------------------|

| <6>   | R | nAck     | version of parallel port <b>nAck</b> signal          |

| <5>   | R | PError   | version of parallel port PError signal               |

| <4>   | R | Select   | version of the parallel port Select signal           |

| <3>   | R | nFault   | version of the parallel port <b>nFault</b> signal    |

| <2:0> | R | reserved | returns undefined when read                          |

|       |   |          |                                                      |

#### dcr

0x002 (Device Control Register)

This register directly controls several output signals as well as enabling some functions. The drivers for nStrobe, nAutoFd, nInit, and nSelectIn are open-collector in mode 000, and are push-pull in all other modes.

In all modes the **dcr** *shall* be able to override any hardware state machine and force the signal active. For example, writing 1s to bits<1:0> *shall* force **nStrobe** and **nAutoFd** low, even in ECP mode. Software will make sure that **dcr** bits <1:0> are set to 0 prior to entering ECP mode.

#### Table 11. Device Control Register

<7:6> R Reserved, returns undefined when read.

| <5> R/W | Direction. |

|---------|------------|

|---------|------------|

| 1: | If <b>mode</b> = 000 or <b>mode</b> = 010, we are standard parallel port and this bit has no effect (drivers are enabled). Otherwise, this bit tri-states the drivers and sets the direction so that data will be read from the peripheral. Note: some designs actually force this bit to a 0 when in modes 000 or 010. Software must be in PS2 mode 001 in order to reliably write this bit to a 1. |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |                                                                                                                                                                                                                                                                                                                                                                                                      |

**0:** Drivers are enabled. DMA, data are written to the peripheral.

#### <4> R/W ackIntEn.

- 1: Enables an interrupt on the rising edge of **nAck**.

- **0:** Disables the **nAck** interrupt.

- <3> R/W Selectin is inverted and then driven as parallel port nSelectin.

- <2> R/W **nInit** is driven as parallel port **nInit**.

- <1> R/W **autofd** is inverted and then driven as parallel port **nAutoFd**.

- <0> R/W **strobe** is inverted and then driven as parallel port **nStrobe**.

#### cFifo

0x400, mode = 010 (Parallel Port Data FIFO)

PWords written or DMAed from the system to this FIFO are transmitted by a hardware handshake to the peripheral using the standard parallel port protocol. Transfers to the FIFO are PWord aligned. If partial PWords need to be transferred then the operation must be handled in mode 000. This mode is only defined for the forward direction.

#### ecpDFifo

0x400, mode = 011 (ECP Data FIFO)

PWords written or DMAed from the system to this FIFO when **direction** is 0 are transmitted to the peripheral by hardware handshake using the ECP parallel port protocol. Transfers to the FIFO are PWord-aligned. If odd bytes need to be transferred, the operation must be handled in mode 000.

Data PWords from the peripheral are read under automatic hardware handshake from ECP into this FIFO when **direction** is 1. Reads or DMAs from the FIFO will return PWords of ECP data to the system.

#### tFifo

0x400, mode = 110 (Test mode)

Data PWords may be read, written, or DMAed to or from the system to this FIFO in any **direction**.

Data in the **tFifo** will not be transmitted to the parallel port lines using a hardware protocol handshake. However, data in the **tFifo** may be displayed on the parallel port data lines.

The **tFifo** will not stall when overwritten or underrun. Data will simply be rewritten or overrun. The **full** and **empty** bits must always keep track of the correct FIFO state. The **tFifo** will transfer data at the maximum ISA rate so that software can generate performance metrics.

The **writeIntrThreshold** can be determined by starting with a **full tFifo**, and emptying it one PWord at a time until **serviceIntr** is set. This may generate a spurious interrupt, but will indicate

that the threshold has been reached. Likewise, **readIntrThreshold** can be determined by setting the direction bit to 1, and filling the **empty tFifo** one PWord at a time until **serviceIntr** is set.

Data PWords are always read from the head of **tFifo**, regardless of the value of the direction bit. For example, if 0x4433, 0x2211, 0x00ff is written to the FIFO, then reading the **tFifo** will return 0x4433, 0x2211, 0x0ff (in the same order it was written).

The FIFO size and interrupt threshold can be determined by writing PWords and checking the **full** and **serviceIntr** bits.

#### cnfgA

<7>

0x400, mode = 111 (Configuration Register A)

This register allows software to obtain implementation-specific information. All ISA ports shall implement the read-only **implD** as a minimum.

#### Table 12. Configuration Register A

- R Indicates if interrupts are pulsed or ISA-Level.

- 1: Interrupts are ISA-Level (See Appendix B).

- 0: Interrupts are ISA-Pulses.

- <6:4> R implD. Implementation ID number; identifies the design and PWord size.

- 0x00: The design is a 16-bit implementation (PWord = 2 bytes).

- 0x01: The design is an 8-bit implementation (PWord = 1 byte).

- 0x02: The design is a 32-bit implementation (PWord = 4 bytes).

0x03-0x07Reserved and not supported by Microsoft Software.

- <3> R/RW **misc. reserved.** May be used for anything design-specific. If software, may try to write it to a 1.

- <2> R **nByteInTransceiver.** This design-dependent, read-only parameter indicates if the design uses an extra pipeline byte when transmitting ECP in event 35. See the section on ECP Host Recovery for more information.

- 0: When transmitting (at event 35) there is 1 byte in the transceiver waiting to be transmitted that does not affect the FIFO **full** bit.

- 1: When transmitting (at event 35) the state of the **full** bit includes the byte being transmitted. There are no extra bytes to be accounted for at abort time.

- <1:0> R/RW This field is a "don't care" for a PWord size of 1 byte. For Host Recovery situations these bits indicate what fraction of a PWord was not transmitted so that software can retransmit the unsent bytes. If the PWord size is 2 or 4 bytes, the value of these two bits is a snapshot of the last PWord being transmitted in mode 011 (event 35) when the FIFO was reset (port was transitioned from mode 011 to mode 000 or 001).

- 00: The PWord at the head of the FIFO contained a complete PWord.

- 01: The PWord at the head of the FIFO contained only 1 valid byte.

- 10: The PWord at the head of the FIFO contained 2 valid bytes.

- 11: The PWord at the head of the FIFO contained 3 valid bytes.

#### cnfgB

0x401, mode = 111 (Configuration Register B)

This register allows software to control the selecting of interrupts and DMA channels. A read-write implementation implies a "software-configurable" device. All ISA ports must implement this as a read-only register as a minimum.

Some or all of the bits may be read-only; for example, if the port is configurable but only supports 8-bit DMA transfers, then <2> will be a read-only bit set to a 0, while <1:0> may be (R/W). Likewise, any or all of the interrupt bits may be read-only.

If a value is not set to 000 (the jumper-default) then it is assumed that the value in the register is correct and software will use this interrupt and/or DMA channel.

#### Table 13. Configuration Register B

| <7>   | R/W          | <b>compress.</b> This is an "optional" feature and need not be implemented. If not implemented, the bit should be read-only and always return a 0 when read. When this bit is 0 compression will not occur. |

|-------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 1:           | When set, this bit causes the sending state machine to compress the data before sending. All devices supporting compression must implement this bit.                                                        |

|       | 0:           | (Default) The transmitter shall send only uncompressed (raw) data in this case.                                                                                                                             |

| <6>   | R            | intrValue. Returns the value on the ISA <b>iRq</b> line to determine possible conflicts.                                                                                                                    |

| <5:3> | R-R/W        | intrLine.                                                                                                                                                                                                   |

|       | 111:         | Selects IRQ 5.                                                                                                                                                                                              |

|       | <b>110</b> : | Selects IRQ 15.                                                                                                                                                                                             |

|       | <b>101</b> : | Selects IRQ 14.                                                                                                                                                                                             |

|       | <b>100</b> : | Selects IRQ 11.                                                                                                                                                                                             |

|       | <b>011</b> : | Selects IRQ 10.                                                                                                                                                                                             |

|       | 010:         | Selects IRQ 9.                                                                                                                                                                                              |

|       | <b>001</b> : | Selects IRQ 7 (default).                                                                                                                                                                                    |

|       | 000:         | If read-only, indicates that the interrupt must be selected with jumpers.                                                                                                                                   |

| <2:0> | R-R/W        | dmaChannel.                                                                                                                                                                                                 |

|       | 111:         | Selects DMA channel 7.                                                                                                                                                                                      |

|       | 110:         | Selects DMA channel 6.                                                                                                                                                                                      |

|       | <b>101</b> : | Selects DMA channel 5 (default, 16-bit).                                                                                                                                                                    |

|       | <b>100</b> : | Indicates jumpered 16-bit DMA if read-only.                                                                                                                                                                 |

|       | <b>011</b> : | Selects DMA channel 3 (default, 8-bit).                                                                                                                                                                     |

|       | <b>010</b> : | Selects DMA channel 2.                                                                                                                                                                                      |

|       |              |                                                                                                                                                                                                             |

- **001**: Selects DMA channel 1.

- **000**: Indicates jumpered 8-bit DMA if read-only.

#### ecr

0x402 (Extended Control Register).

This register controls the extended ECP/parallel port functions.

#### Table 14. Extended Control Register

- <7:5> R/W mode

- **000:** Standard Parallel Port mode. In this mode the FIFO is reset and common collector drivers are used on the control lines (**nStrobe**, **nAutoFd**, **nInit**, and **nSelectIn**). Setting the **direction** bit will not tri-state the output drivers in this mode.

- **001**: *PS/2 Parallel Port mode.* Same as above except that **direction** may be used to tri-state the **data** lines, and reading the **data** register returns the value on the **data** lines and not the value in the **data** register. It is always best for the hardware design to read the value of the lines and not the register. (Some old Centronics interfaces actually returned the reg value and not the wire value.) All drivers have active pull-ups (push-pull).

- 010: Parallel Port FIFO mode. This is the same as 000 except that PWords are written or DMAed to the FIFO. FIFO data is automatically transmitted using the standard parallel port protocol. Note that this mode is only useful when direction is 0. All drivers have active pull-ups (push-pull).

- **011:** *ECP Parallel Port mode.* In the forward direction (**direction** is 0), PWords placed into the **ecpDFifo** and bytes written to the **ecpAFifo** are placed in a single FIFO and transmitted automatically to the peripheral using ECP

Protocol. In the reverse direction (**direction** is 1), bytes are moved from the ECP parallel port and packed into PWords in the **ecpDFifo**. All drivers have active pull-ups (push-pull).

- **100**: Vendor-specified function.

- **101**: Vendor-specified function.

- **110**: *Test mode*. In this mode the FIFO may be written and read, but the data will not be transmitted on the parallel port.

- **111**: *Configuration mode*. In this mode the **cnfgA** and **cnfgB** registers are accessible at 0x400 and 0x401.

- <4> R/W **nErrIntrEn** (valid only in ECP mode)

- 1: Disables the interrupt generated on the asserting edge of **nFault**.

- 0: Enables an interrupt pulse on the high to low edge of **nFault**. Note that an interrupt will be generated if **nFault** is asserted (interrupting) and this bit is written from a 1 to a 0. This prevents interrupts from being lost in the time between the read of the **ecr** and the write of the **ecr**.

#### <3> R/W dmaEn

- 1: Enables DMA (DMA starts when **serviceIntr** is 0).

- **0**: Disables DMA unconditionally.

#### <2> R/W serviceIntr

- 1: Disables DMA and all of the service interrupts.

- **0:** Enables one of the following 3 cases of interrupts. Once one of the 3 service interrupts has occurred, **serviceIntr** bit shall be set to a 1 by hardware. Writing this bit to a 1 will not cause an interrupt.

| case<br>dmaEn=1:                | During DMA (this bit is set to a 1 when terminal count is reached).                                                   |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| case<br>dmaEn=0<br>direction=0: | This bit shall be set to 1 whenever there are writeIntrThreshold or more PWords free in the FIFO.                     |

| case<br>dmaEn=0<br>direction=1: | This bit shall be set to 1 whenever there are <b>readIntrThreshold</b> or more valid PWords to be read from the FIFO. |

#### <1> R full

- 1: **direction** = 0. The FIFO cannot accept another PWord.

- 1: direction = 1. The FIFO is completely full.

- **0:** direction = 0. The FIFO has at least 1 free PWord.

- **0:** direction = 1. The FIFO has at least 1 free byte.

#### <0> R empty

- 1: **direction** = 0. The FIFO is completely empty.

- 1: direction = 1. The FIFO contains less than 1 PWord of data.

- **0:** direction = 0. The FIFO contains at least 1 byte of data.

- **0: direction** = 1. The FIFO contains at least 1 PWord of data.

#### Operation

#### Interrupts

An interrupt shall be generated in the following cases:

- When **serviceIntr** is 0, **dmaEn** is 1, and the DMA reaches a terminal count.