# CB-C7, 3-VOLT 0.8-MICRON CELL-BASED CMOS ASIC

Preliminary October 1993

# **Description**

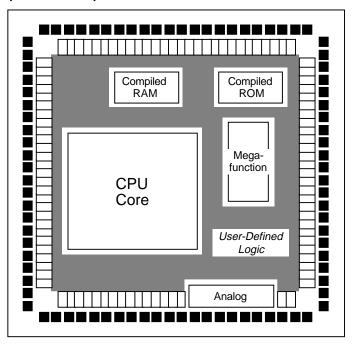

The CB-C7, 3-volt cell-based product family is intended for low power portables and battery-operated products. A power reduction of up to 60 percent is now possible compared with the CB-C7, 5-volt. The CB-C7, 3-volt is manufactured with a 0.8-micron (drawn) process with two-or three-layer metalization and is offered in 22 I/O ring sizes. Typical applications include handheld terminals, personal digital office assistants, word spellers, cellular phones and a variety of high-volume, portable PC-based applications. The family allows designing complex logic functions, up to 237,000 usable gates of user-defined logic. Megamacro blocks may include industry-standard CPU cores, peripherals, and analog functions — thus enabling complete system-on-a-chip solutions.

The CB-C7 series consists of two types of architectures, a Fast Turn FT-type embedded array and a High Density HD-type full standard cell. The FT-type uses fully-diffused standard cell embedded cores with sea-of-gates user-definable logic. The FT solution offers gate-array-like turn-around times while allowing the incorporation of large embedded functions. Another important advantage is that the FT-type is well-suited for multiple designs built around a common embedded CPU function, such as the V30HL (8086) CPU.

The HD-type is comprised of fully-diffused standard cell architecture for both the embedded cores and the user-defined logic area. This solution offers an optimal die size for economic cost-effective volume production. Full gate delay models are available for both in Verilog<sup>®</sup>, a golden simulator, as part of NEC's OpenCAD<sup>®</sup> Design System.

### **Features**

- □ Low voltage cell-based library means power savings of up to 60% over 5V solutions

- □ 1.6 µW/gate per MHz power dissipation at 3 V

- ☐ Standby current I<sub>DDO</sub> < 150 nA

- Advanced 0.8 μ drawn gate (0.6 μ L<sub>eff</sub>) length CMOS technology with three-layer metalizations

- Up to 237,000 usable gates on 3-layer HD full standard cell product with 440 I/Os and a pad pitch of 124 μm

- ☐ Extensive embedded core library includes CPU, analog, and video DAC functions

- ☐ Datapath compiler available for multipliers, FIFOs, and register files

- □ Supports leading third-party design tools

Figure 1. Integrated HDD Solution with CB-C7 Cell-Based ASIC and Embedded Megafunctions

# **Digital Megamacros in Library**

| Compatible Device | NEC<br>Code      | Description                      |

|-------------------|------------------|----------------------------------|

| 8088              | V20HL (NA70108H) | 8-bit CPU                        |

| 8086              | V30HL (NA70116H) | 16-bit CPU                       |

| Z80               | NA70008A         | Z80™ 8-bit CPU                   |

| 80C42             | NA80C42H         | Keyboard Controller              |

| 8237A             | NA71037          | Programmable DMA Controller      |

| 8251A             | NA71051          | Serial Communications Controller |

| 8254              | NA71054          | Interval Timer                   |

| 8255A             | NA71055          | Peripheral Interface             |

| 8259A             | NA71059          | Interrupt Controller             |

| 4991A             | NA4991A          | Real Time Clock                  |

| 72020             | NA72020          | Graphics Display Controller      |

# **Analog Megamacros in Library**

| NEC      |                                     |

|----------|-------------------------------------|

| Code     | Description                         |

| XXXA     | 135 MHz triple 8-bit video DAC      |

| AADA8GPC | 8-bit general-purpose DAC           |

| AACP25NA | High-speed (25ns) comparator        |

| AACP80NA | High-speed (80ns) comparator        |

| AACP01UA | General-purpose comparator          |

| AAOP10MA | High-speed operational amplifier    |

| AAOP01MA | General-purpose operative amplifier |

| AASWGPCA | Analog switch with control          |

| AASWGPTA | Analog switch with control          |

Note: Some analog functions are currently in development

# **OpenCAD Design System**

CB-C7 is supported by the OpenCAD Design System, an ASIC design environment that merges the best of today's most powerful CAD ASIC software design tools and proprietary tools, such as a floorplanner and module compilers, into a single environment.

Sample design kits are available at no charge to qualified users: contact the NEC ASIC Design Center nearest you for more information. A software license agreement is required.

### **Digital Megafunctions**

In addition to the V30HL/V20HL 8086, 8088 product families and support peripherals, NEC offers complex standard IC functions as well as A/D and D/A converters for multimedia applications. Compiled RAM and ROM are also available to satisfy a myriad of different product applications.

### **Analog Blocks**

NEC is building upon its expertise in analog standard ICs by now offering select members of its analog family as analog megamacros. These megamacros are layed out in the I/O area to maximize die area in the core for digital functions and user-defined logic. This separation of the analog and digital functions and separate analog  $\rm V_{DD}$  and  $\rm V_{SS}$  line also contributes to better noise isolation.

Digital and analog functions on a CB-C7 cell-based array are tested separately.

### Test and Emulation Bus Architecture

The test and emulation bus architecture used for CB-C7 design methodology approach to the testing and emulation of embedded functions. It allows the emulation of the production chip for system validation, reuse of the test bus circuit and use of standard micro IC functional test vectors and system vectors in a modularized fashion. It also provides real-time emulation support and its test bus structure allows testing of on-chip RAM/ROM or analog blocks.

# **On-Chip Compiled Memory**

RAM and ROM blocks can be custom compiled in the CB-C7 design environment.

The RAM and ROM compiler allows ASIC designers to generate silicon-efficient memory blocks of specific size and performance to suit exact system requirements quickly and efficiently.

The table of compilable RAM and ROM, shown on page 4, describes three different MUX ratios along with the minimum and maximum size. For the 16:1 MUX, the minimum word depth is 256 and the minimum bit width is 1. The word depth can increase by 64 words in increments up to 2K and the bit width can increase by 1 bit up to a maximum of 8 bits. The other RAM and ROM configurations are determined in the same fashion.

Typical examples of applications containing digital memory and analog cores and their step size is shown in Figure 2.

### 3 V Operation

CB-C7 CMOS is ideal for low power, high volume, battery-operated products. The CB-C7 process has been recharacterized to operate at two voltage levels, 5 V  $\pm$  10% and 3.0 V  $\pm$  10%. Not only have macrocells been recharacterized to operate at the lower voltage, but complex megamacros and compiled memory as well.

Figure 2. Typical Application Example (See Table 2)

#### **Trademarks**

- ®OpenCAD is a registered trademark of NEC Electronics

- $^{\text{TM}}Z80$  is a trademark of Zilog, Inc.

- <sup>®</sup>Verilog is a registered trademark of Cadence Design System, Inc.

- ™MACRObus is a trademark of NEC Electronics Inc.

Table 1. CB-C7 Step Sizes and Usable Gate Count

|     |           |                  |                 | HD-Type Usable Gates <sup>2</sup> |               | FT-Type Usa   | ble Gates <sup>2</sup> |

|-----|-----------|------------------|-----------------|-----------------------------------|---------------|---------------|------------------------|

| No. | Step Size | I/O <sup>1</sup> | Total Raw Grids | 2-Layer Metal                     | 3-Layer Metal | 2-Layer Metal | 3-Layer Metal          |

| 1   | B18       | 88               | 35,400          | 5,930                             | 7,040         | 3,140         | 3,860                  |

| 2   | B57       | 104              | 49,600          | 8,840                             | 10,430        | 4,720         | 5,760                  |

| 3   | B97       | 120              | 66,600          | 12,390                            | 14,560        | 6,660         | 8,070                  |

| 4   | C37       | 136              | 86,000          | 16,530                            | 19,370        | 8,910         | 10,760                 |

| 5   | C76       | 152              | 107,700         | 21,150                            | 24,740        | 11,440        | 13,780                 |

| 6   | D16       | 168              | 131,800         | 26,460                            | 30,900        | 14,340        | 17,230                 |

| 7   | D55       | 184              | 158,300         | 32,230                            | 37,590        | 17,490        | 20,990                 |

| 8   | D75       | 192              | 172,500         | 35,390                            | 41,260        | 19,230        | 23,050                 |

| 9   | E15       | 208              | 202,700         | 42,160                            | 49,100        | 22,930        | 27,450                 |

| 10  | E54       | 224              | 235,800         | 49,360                            | 57,440        | 26,870        | 32,140                 |

| 11  | E94       | 240              | 270,800         | 57,290                            | 66,630        | 31,220        | 37,300                 |

| 12  | F34       | 256              | 307,800         | 65,810                            | 76,500        | 35,890        | 42,850                 |

| 13  | F74       | 272              | 348,300         | 74,730                            | 86,820        | 40,780        | 48,660                 |

| 14  | G14       | 288              | 390,700         | 84,410                            | 98,030        | 46,100        | 54,970                 |

| 15  | G53       | 304              | 435,500         | 94,480                            | 109,680       | 51,620        | 61,520                 |

| 16  | G93       | 320              | 482,100         | 105,330                           | 122,240       | 57,580        | 68,590                 |

| 17  | H33       | 336              | 531,700         | 116,770                           | 135,470       | 63,860        | 76,040                 |

| 18  | H72       | 352              | 583,800         | 128,550                           | 149,100       | 70,330        | 83,710                 |

| 19  | J32       | 376              | 662,900         | 147,680                           | 171,230       | 80,830        | 96,170                 |

| 20  | J71       | 392              | 720,900         | 160,890                           | 186,510       | 88,090        | 104,770                |

| 21  | K11       | 408              | 781,300         | 174,960                           | 202,780       | 95,820        | 113,930                |

| 22  | K90       | 440              | 907,800         | 204,550                           | 236,990       | 112,070       | 133,200                |

- Notes: 1. I/O may be configured as VDD/GND

- 2. Usable gates: equivalent estimated 2-input NAND, will vary depedning ons pecific design

a. 2-layer metal FT = 55% utilization for routing HD = 65% utilization for routing FT = 65% utilization for routing b. 3-layer metal HD = 75% utilization for routing

c. Grid/gate ratio\* FT = 4.3 grid/gate ratio HD = 2.8

d. Grid to gate ratio based on conversion from other libraries will be different. Contact NEC Design Center for die size estimation

Based on CMOS-6 L302 cell equivalents

Table 2. Examples of Core Use (Refer to Figure 2)

| Application         | Core                                          | UDL*   | I/O | Step Size | Metalization | Package  |

|---------------------|-----------------------------------------------|--------|-----|-----------|--------------|----------|

| Cellular Phone      | Z80                                           | 40,000 | 102 | E94       | 3LM          | 120 TQFP |

| Wireless or GPS     | V20HL                                         | 10,000 | 88  | D55       | 3LM          | 100 TQFP |

| Hard Disk Drive     | V20HL<br>71054<br>71059                       | 3,000  | 80  | D55       | 2LM          | 100 TQFP |

| Graphics Controller | Triple Video DAC<br>HS RAM 256 W x 8 bits x 3 | 40,000 | 182 | E94       | 3LM          | 208 PQFP |

| Document Scanner    | ROM 256 W x 16 bits<br>RAM 64W x 8 bits x 5   | 3,000  | 88  | C37       | 2LM          | 100 QFP  |

<sup>\*</sup> UDL = User-Defined Logic; measured in 2-input NAND gate equivalents of CMOS-6 family

# Table 3. Compilable RAM, ROM and Datapath Elements for CB-C7

| Compiled SRAM                                           |           |          |                 |  |  |  |

|---------------------------------------------------------|-----------|----------|-----------------|--|--|--|

| <ul> <li>Single port, asynchronous operation</li> </ul> |           |          |                 |  |  |  |

|                                                         | Increment |          |                 |  |  |  |

| 16:1 Column MUX                                         | 256 x 1   | 2K x 8   | 64 words, 1 bit |  |  |  |

| 8:1 Column MUX                                          | 128 x 1   | 1K x 16  | 32 words, 1 bit |  |  |  |

| 4:1 Column MUX                                          | 64 x 1    | 512 x 32 | 16 words, 1 bit |  |  |  |

|                                                         |           |          | _               |  |  |  |

### **Compiled High-Speed SRAM**

- Single port, asynchronous high speed operation

- Speed: 12.6ns (typ) (512W x 8 bit)

|                         | Min Size    | Max Size       | Increment         |

|-------------------------|-------------|----------------|-------------------|

| 8:1 Column MUX          | 16 x 1      | 2K x 20        | 16 words, 1 bit   |

| Example: For a 8:1 colu | ımn MUX min | imum size is 1 | 6 x 1. Increments |

Example: For a 8:1 column MUX minimum size is 16 x 1. Increments can thus be 16, 32, 48 words up to 2K max. Bit size can be a minimum of 1 bit, one bit at time increments to 20 bits max.

Examples for Compiled High-Speed SRAM: For a 8:1 column MUX, minimum size is 16 x 1. Increments can thus be 16, 32, 48, words up to 2K max. Bit size can be minimum of 1 bit, one bit at a time in increments to 20 bits max.

| Compiled Dual Port RAM            |                 |                |                      |  |  |  |

|-----------------------------------|-----------------|----------------|----------------------|--|--|--|

| Dual port, asynchronous operation |                 |                |                      |  |  |  |

|                                   | , ,             | •              |                      |  |  |  |

| – Sp                              | eea: 43ns (ty)  | o) (512W x 8 b | oit)                 |  |  |  |

|                                   | Min Size        | Max Size       | Increment            |  |  |  |

| 8:1 Column MUX                    | 16 x 1          | 2K x 32        | 16 words, 1 bit      |  |  |  |

|                                   | Compile         | d ROM          |                      |  |  |  |

| – Sir                             | ngle port, asyr | nchronous ope  | ration               |  |  |  |

| - Sp                              | eed: 63ns (typ  | o) (512W x 8 b | oit)                 |  |  |  |

|                                   | Min Size        | Max Size       | Increment            |  |  |  |

| 32:1 Column MUX                   | 512 x 1         | 32K x 16       | 512 words,<br>1 bit  |  |  |  |

| 16:1 Column MUX                   | 256 x 2         | 16K x 32       | 256 words,<br>1 bit  |  |  |  |

| 8:1 Column MUX                    | 128 x 4         | 8K x 64        | 128 words,<br>2 bits |  |  |  |

|                                   | Datapath        | Modules        |                      |  |  |  |

|                                   | Min Size        | Max Size       | Increment            |  |  |  |

| Multiplier                        | 6 x 6           | 32 x 32        | 2 bits               |  |  |  |

| Register File                     | 8 x 2           | 256 x 32       | 4 words, 1 bit       |  |  |  |

| FIFO                              | 8 x 2           | 256 x 32       | 2 words, 1 bit       |  |  |  |

<sup>\*</sup> Please check with the Design Center for exact specifications and availability.

# **Absolute Maximum Ratings**

| Power supply voltage, V <sub>DD</sub>                 | -0.5 to +6.5 V                    |

|-------------------------------------------------------|-----------------------------------|

| Input/output voltage, V <sub>I</sub> / V <sub>O</sub> | -0.5 V to V <sub>DD</sub> + 0.5 V |

| Output current, I <sub>O</sub>                        |                                   |

| $I_{OL}$ (min) = 2.2 mA (typ)                         | 8 mA                              |

| $I_{OL}$ (min) = 4.4 mA (typ)                         | 16 mA                             |

| $I_{OL}$ (min) = 6.6 mA (typ)                         | 24 mA                             |

| Operating temperature, T <sub>OPT</sub>               | -40 to +85°C                      |

| Storage temperature, T <sub>STG</sub>                 | −65 to +150°C                     |

**Caution:** Exposure to absolute maximum ratings for extended periods may affect device reliability; exceeding the ratings could cause permanent damage. The device should not be operated outside the recommended operating conditions.

# **Input/Output Capacitance**

$V_{DD} = V_{I} = 0 \text{ V}; f = 1 \text{ MHz}$

| Terminal | Symbol           | Тур | Max | Unit |

|----------|------------------|-----|-----|------|

| Input    | C <sub>IN</sub>  | 10  | 20  | pF   |

| Output   | C <sub>OUT</sub> | 10  | 20  | pF   |

| I/O      | C <sub>I/O</sub> | 10  | 20  | pF   |

#### Note:

(1) Values include package pin capacitance.

# **Power Consumption**

| Description         | Limits (max) | Unit   | Test Conditions   |

|---------------------|--------------|--------|-------------------|

| Internal cell (L30) | 2) 1.6       | μW/MHz | F/O = 2; L = 2 mm |

# **Recommended Operating Conditions**

| Parameter                                       | Symbol                            | Min                 | Max             | Unit |

|-------------------------------------------------|-----------------------------------|---------------------|-----------------|------|

| Power supply voltage                            | $V_{DD}$                          | 2.7                 | 3.3             | V    |

| Ambient temperature                             | T <sub>A</sub>                    | - 40                | +85             | °C   |

| Input voltage                                   | V <sub>I</sub>                    | 0                   | V <sub>DD</sub> | V    |

| High-level input voltage                        | V <sub>IH</sub>                   | 0.7 V <sub>DD</sub> | V <sub>DD</sub> | V    |

| Low-level input voltage                         | V <sub>IL</sub>                   | 0.3 V <sub>DD</sub> | V <sub>DD</sub> | V    |

| Input rise or fall time (normal input)          | t <sub>RI</sub> , t <sub>FI</sub> | 0                   | 200             | ns   |

| Input rise or fall time (Schmitt-trigger input) | t <sub>RI</sub> , t <sub>FI</sub> | 0                   | 10              | ms   |

| Positive Schmitt-trigger voltage                | V <sub>P</sub>                    | 1.8                 | 4.0             | V    |

| Negative Schmitt-trigger voltage                | V <sub>N</sub>                    | 0.6                 | 3.1             | V    |

| Hysteresis voltage                              | V <sub>H</sub>                    | 0.3                 | 1.5             | V    |

**Note:** The rise/fall time given for a Schmitt-trigger input buffer varies depending on the operating environment. Simultaneous switching of output buffers should be analyzed before deciding to use a Schmitt-trigger input buffer.

### **AC Characteristics**

$V_{DD} = 3 \text{ V} \pm 10\%; \ T_{A} = -40 \text{ to } +85^{\circ}\text{C}$

| Parameter                      | Symbol           | Min | Тур       | Max | Unit | Conditions                                  |

|--------------------------------|------------------|-----|-----------|-----|------|---------------------------------------------|

| Internal toggle frequency      | f <sub>TOG</sub> | 52  |           |     | MHz  | D-F/F; F/O = 2                              |

| Delay time, 2-input NAND Gate* |                  |     |           |     |      |                                             |

| Standard gate (F302) HD-type   | t <sub>PD</sub>  |     | 520 (HL)  |     | ps   | F/O = 1; L = 2 mm                           |

| Standard gate (F302) HD-type   | t <sub>PD</sub>  |     | 870 (HL)  |     | ps   | F/O = 2; L = 1 mm                           |

| Low power gate (L302) HD-type  | t <sub>PD</sub>  |     | 680 (HL)  |     | ps   | F/O = 1; L = 0 mm                           |

| Low power gate (L302) HD-type  | t <sub>PD</sub>  |     | 1310 (HL) |     | ps   | F/O = 2; L = 1 mm                           |

| Delay time, Buffer             |                  |     |           |     |      |                                             |

| Input buffer (FI01)            | t <sub>PD</sub>  |     | 760       |     | ps   | F/O = 2; L = 2 mm                           |

| Output buffer (FO01)           | t <sub>PD</sub>  |     | 4800      |     | ps   | $C_L = 15 \text{ pF}, IOL = 4\text{mA}$     |

| Rise and Fall Times            |                  |     |           |     |      |                                             |

| Output rise time (FO01)        | t <sub>R</sub>   |     | TBD       |     | ps   | $C_L = 15 \text{ pF, IOL} = 2.2 \text{ mA}$ |

| Input fall time (FO01)         | $t_{F}$          |     | TBD       |     | ps   | C <sub>L</sub> = 15 pF, IOH= -2mA           |

<sup>\*</sup> With L101 as load

5

DC Characteristics  $V_{DD} = 3 \text{ V} \pm 10\%; T_A = -40 \text{ to } +85^{\circ}\text{C}$

| Parameter                        | Symbol          | Min                  | Тур               | Max | Unit | Conditions                |

|----------------------------------|-----------------|----------------------|-------------------|-----|------|---------------------------|

| Static current (Note 1)          | I <sub>L</sub>  |                      | TBD               | TBD | μA   | $V_I = V_{DD}$ or GND     |

| Input leakage current            |                 |                      |                   |     |      |                           |

| Normal input                     | I <sub>I</sub>  |                      | ±10 <sup>-5</sup> | ±8  | μΑ   | $V_I = V_{DD}$ or GND     |

| 50 kΩ pull-up                    | I <sub>I</sub>  | TBD                  | TBD               | TBD | μΑ   | $V_I = GND$               |

| 5 kΩ pull-up                     | I <sub>I</sub>  | TBD                  | TBD               | TBD | mA   | V <sub>I</sub> = GND      |

| 50 kΩ pull-down                  | I <sub>I</sub>  | TBD                  | TBD               | TBD | μΑ   | $V_I = V_{DD}$            |

| Off-state output leakage current |                 |                      |                   |     |      |                           |

| Normal Input                     | I <sub>OZ</sub> |                      | ±10 <sup>-5</sup> | ± 8 | μA   | $V_O = V_{DD}$ or GND     |

| 50 kΩ pull-up                    | I <sub>OZ</sub> | TBD                  | TBD               | TBD | μA   | V <sub>I</sub> = GND      |

| 5 kΩ pull-up                     | I <sub>OZ</sub> | TBD                  | TBD               | TBD | μA   | V <sub>I</sub> = GND      |

| 50 kΩ pull-down                  | I <sub>oz</sub> | TBD                  | TBD               | TBD | μA   | $V_I = V_{DD}$            |

| Low-level output voltage (CMOS)  |                 |                      |                   |     |      |                           |

|                                  | V <sub>OL</sub> |                      |                   | 0.4 | V    | I <sub>OL</sub> = 2.2mA   |

|                                  | V <sub>OL</sub> |                      |                   | 0.4 | V    | I <sub>OL</sub> = 4.4 mA  |

|                                  | V <sub>OL</sub> |                      |                   | 0.4 | V    | I <sub>OL</sub> = 6.6 mA  |

| High-level output voltage        | V <sub>OH</sub> | V <sub>DD</sub> -0.4 |                   |     | V    | I <sub>OH</sub> = -1.1mA  |

|                                  | V <sub>OH</sub> | V <sub>DD</sub> -0.4 |                   |     | V    | I <sub>OH</sub> = -2.2mA  |

|                                  | V <sub>OH</sub> | V <sub>DD</sub> -0.4 |                   |     | V    | $I_{OH} = -3.3 \text{mA}$ |

### Notes:

<sup>(1)</sup> The maximum value reflects the use of pull-up/pull-down resistors and oscillator blocks. Contact an NEC ASIC Design Center for assistance in calculation.

<sup>(2)</sup> CMOS-level output buffer (V<sub>DD</sub> = 5 V  $\pm$  10%, T<sub>A</sub>= -40°C to +85°C)

Table 4. Package Options

| Pad Ring Step Sizes                        | B18 | B57 | B97 | C37 | C76 | D16 | D55 | D75 | E15 | E54 | E9 |

|--------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|

| Package Type                               |     |     |     |     |     |     |     |     |     |     |    |

| Plastic Quad Flatpack (QFP)                |     |     |     |     |     |     |     |     |     |     |    |

| 44-pin (0.8 mm lead pitch)                 | Α   | Α   | А   | Α   | Α   | Α   | _   | _   | _   | -   | _  |

| 52-pin (1 mm lead pitch)                   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | _   | _   | -   | _  |

| 64-pin (1 mm lead pitch)                   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α  |

| 80-pin (0.8 mm lead pitch)                 | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α  |

| 100-pin (0.65 mm lead pitch)               | _   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | A  |

| 120-pin (0.8 mm lead pitch)                | -   | _   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α  |

| 136-pin (0.65 mm lead pitch)               | _   | _   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | A  |

| 160-pin (0.65 mm lead pitch)               | _   | _   | _   | _   | _   | Α   | Α   | Α   | Α   | Α   | A  |

| 160 <sup>1</sup> -pin (0.65 mm lead pitch) | _   | _   | _   | _   | _   | _   | _   | Α   | Α   | Α   | A  |

| 160 <sup>2</sup> -pin (0.65 mm lead pitch) | -   | _   | -   | _   | -   | -   | -   | Α   | Α   | Α   | A  |

| Plastic Quad Flatpack (QFP-FP)             |     |     |     |     |     |     |     |     |     |     |    |

| 100-pin (0.5 mm lead pitch)                | -   | Α   | А   | Α   | Α   | Α   | А   | Α   | Α   | Α   | /  |

| 120-pin (0.5 mm lead pitch)                | -   | -   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | ,  |

| 144-pin (0.5 mm lead pitch)                | -   | _   | _   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | 1  |

| 160-pin (0.5 mm lead pitch)                | _   | _   | _   | _   | _   | Α   | Α   | Α   | Α   | Α   | ,  |

| 160 <sup>2</sup> -pin (0.5 mm lead pitch)  | _   | _   | _   | _   | _   | _   | _   | Α   | Α   | Α   | ,  |

| 176-pin (0.5 mm lead pitch)                | -   | _   | -   | -   | -   | Α   | Α   | Α   | Α   | Α   | 1  |

| 1761-pin (0.5 mm lead pitch)               | _   | _   | _   | _   | _   | _   | _   | _   | _   | Α   | ,  |

| 176 <sup>2</sup> -pin (0.5 mm lead pitch)  | _   | _   | _   | _   | _   | _   | _   | _   | _   | Α   | ,  |

| 208-pin (0.5 mm lead pitch)                | _   | -   | -   | -   | -   | -   | -   | -   | -   | -   | ,  |

| Thin Plastic Quad Flatpack (TQF            | Р)  |     |     |     |     |     |     |     |     |     |    |

| 64-pin (0.5 mm lead pitch)                 | Α   | Α   | Α   | Α   |     |     |     | _   |     |     | -  |

| 80-pin (0.5 mm lead pitch)                 | Α   | Α   | Α   | Α   | _   | _   | _   | _   | _   | _   | -  |

| 1001-pin (0.5 mm lead pitch)               | -   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | -   | -  |

| Plastic Leaded Chip Carrier (PLC           | CC) |     |     |     |     |     |     |     |     |     |    |

| 68-pin (50 mils lead pitch)                | _   | _   | _   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | -  |

| 84-pin (50 mils lead pitch)                | _   | _   | _   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | -  |

<sup>1 =</sup> Cu lead frame

**Note:** NEC reserves the right to alter these package options based on the results of qualification. Each cell-based design/package combination must be cleared for manufacturing suitability. For the latest package availability for CB-C7, please contact your local NEC ASIC Design Center.

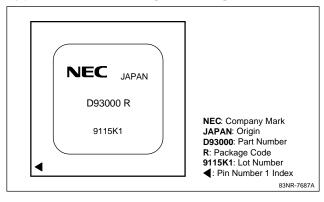

# Typical CB-C7 Package Marking

### CB-C7 Numbering System

| Part Number | Description                                                                     |

|-------------|---------------------------------------------------------------------------------|

| μPD93XXX    | Contains logic only or logic plus RAM and/or ROM                                |

| μPD94XXX    | Contains the same as µPD93XXX but with ROM code change                          |

| μPD95XXX    | Same as µPD93XXX but contains megamacro blocks, such as a 710XXX or V20HL/V30HL |

| μPD96XXX    | Same as µPD95XXX but with a ROM code change                                     |

A = Available or under development

<sup>2 =</sup> Cu lead frame and heat sink

<sup>- =</sup> Unavailable

Table 4. Package Options (Cont'd)

| Pad Ring Step Size                         | F34 | F74 | G14 | G53 | G93 | H33 | H72 | J32 | J71 | K11 | K90 |

|--------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Package Type                               |     |     |     |     |     |     |     |     |     |     |     |

| Plastic Quad Flatpack (QFP)                |     |     |     |     |     |     |     |     |     |     |     |

| 64-pin (1 mm lead pitch)                   | Α   | -   | -   | _   | _   | _   | _   | -   | _   | _   | _   |

| 80-pin (0.8 mm lead pitch)                 | Α   | -   | -   | -   | -   | -   | -   | -   | -   | _   | -   |

| 100-pin (0.65 mm lead pitch)               | Α   | -   | -   | -   | _   | -   | -   | -   | -   | -   | -   |

| 120-pin (0.8 mm lead pitch)                | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | _   | _   | _   |

| 136-pin (0.65 mm lead pitch)               | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | _   | _   | _   |

| 160-pin (0.65 mm lead pitch)               | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | A   |

| 160¹-pin (0.65 mm lead pitch)              | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | A   |

| 160 <sup>2</sup> -pin (0.65 mm lead pitch) | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | A   |

| 184¹-pin (0.65 mm lead pitch)              | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | A   |

| Plastic Quad Flatpack (QFP-FP)             |     |     |     |     |     |     |     |     |     |     |     |

| 100-pin (0.5 mm lead pitch)                | Α   | Α   | _   | _   | _   | _   | _   | _   | _   | _   | -   |

| 120-pin (0.5 mm lead pitch)                | Α   | Α   | Α   | Α   | Α   | Α   | Α   | _   | _   | _   | -   |

| 144-pin (0.5 mm lead pitch)                | Α   | Α   | Α   | Α   | Α   | Α   | Α   | -   | -   | -   | -   |

| 160-pin (0.5 mm lead pitch)                | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | A   |

| 160 <sup>2</sup> -pin (0.5 mm lead pitch)  | Α   | Α   | Α   | Α   | Α   | Α   | Α   | _   | _   | _   | -   |

| 176-pin (0.5 mm lead pitch)                | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | 1   |

| 1761-pin (0.5 mm lead pitch)               | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | ,   |

| 176 <sup>2</sup> -pin (0.5 mm lead pitch)  | Α   | Α   | Α   | Α   | Α   | Α   | Α   | _   | _   | _   | -   |

| 208-pin (0.5 mm lead pitch)                | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | /   |

| 2081-pin (0.5 mm lead pitch)               | _   | _   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | ,   |

| 208 <sup>2</sup> -pin (0.5 mm lead pitch)  | _   | _   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | ,   |

| 240¹-pin (0.5 mm lead pitch)               | -   | _   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | 1   |

| 256¹-pin (0.4 mm lead pitch)               | _   | _   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | ,   |

| 272 <sup>1</sup> -pin (0.5 mm lead pitch)  | _   | _   | _   | _   | _   | _   | _   | Α   | Α   | Α   | A   |

| 304¹-pin (0.5 mm lead pitch)               | _   | _   | _   | _   | _   | _   | _   | _   | _   | Α   | ,   |

<sup>1 =</sup> Cu lead frame

A = Available or under development

- = Unavailable

**Note:** NEC reserves the right to alter these package options based on the results of qualification. Each cell-based design/package combination must be cleared for manufacturing suitability. For the latest package availability for CB-C7, please contact your local NEC ASIC Design Center.

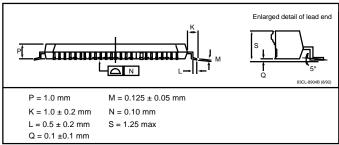

Figure 3. Popular CB-C7 Package 100-pin TQFP — ■14 mm Body Size

<sup>2 =</sup> Cu lead frame and heat sink

# **NEC's ASIC Design System**

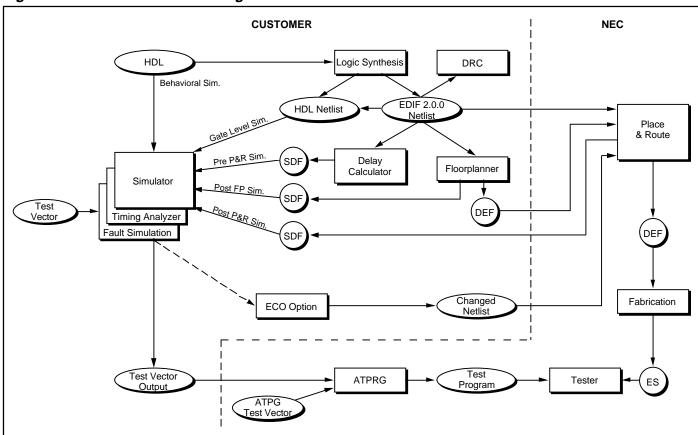

NEC supports its ASIC products with a comprehensive CAD system that significantly reduces the time and expense usually associated with the development of semi-custom devices. NEC's OpenCAD Design System is a front-end to back-end ASIC design package that merges several advanced CAE/CAD tools into a single structure. The design flow combines tools for floorplanning, logic synthesis, automatic test generation, accelerated fault-grading, full timing simulation, and advanced place-and-route algorithms. RAM/ROM and Datapath Compilers are also available for use in CB-C7 designs.

A top-down modeling methodology is possible by means of HDL specification. Designers can concentrate their design effort at a higher level of abstraction, specifying, modeling, and simulating their designs at a systems level. This leaves the details of the gate-level implementation to the synthesis tools. After having verified proper functionality, designers are free to explore functional and architectural trade-offs, and can optimize chip performance while minimizing chip area. An engineer can

evaluate several architectures and select the best solution before committing to silicon. The design flow is shown below.

One of the key benefits of the ASIC design flow is that sign-off simulation can be accomplished at the customer's site since NEC offers designers a choice of simulators with the "golden simulator" status. Golden simulator status means that after receiving the post place-and-route simulation results from the customer, NEC can proceed directly to photomask production, bypassing the additional post-simulation steps.

To simplify simulation and testing of embedded cores and megamacros, full Verilog gate delay models are provided for all megamacros. The megamacros are then fully tested with a standard set of production test vectors.

The floorplanner tool provides a realistic estimate of wire length by grouping hierarchical blocks in a specific physical location on the chip. This allows for more accurate simulation results by minimizing critical path interconnect delays. The floorplanner also allows for placement of fully-diffused functions such as memory

Figure 4. CB-C7 HDL-Based Design Flow

and microprocessors. Graphical I/O assignment is available with the floorplanner. The floorplanner generates a delay file for post-floorplanner simulation, as shown in the design flow.

The ECO option allows the designer to make minor corrections in the design without requiring an entirely new placement and routing of the device. The tool ensures that relatively small changes, such as connectivity changes, will not greatly impact the timing of the current design. This can vastly improve turnaround time for the design.

NEC also incorporates proprietary tools to facilitate the design process. A single delay calculator is used for all CAE platforms to ensure consistent timing and simula-

tion results. A comprehensive design rule check, DRC, program reports design rule violations as well as chip utilization statistics for the design netlist. The generated report contains information such as cell count and usage rate as well as net and total pin counts. Unused input pins, violations in pin naming conventions, and exceeded fan-out limits are examples of the design rule violations reported by this program.

Sample design kits are available at no charge to qualified users: Contact an NEC ASIC design center for more information. NEC's ASIC Design Centers are listed on the back of this data sheet. A software license agreement is required.

# **Cell Library List**

The CB-C7 standard cell library offers a variety of blocks, macrocells and megafunctions. SSI library elements shown include gates, flip-flop circuits, and shift registers. The names and functions of these blocks are designed to be compatible with those of the CMOS-7 and CMOS-6 families.

### **Block List**

| Block<br>Name | Description                                                      | I <sub>OL</sub><br>(mA) | Area <sup>1</sup><br>(grids) |

|---------------|------------------------------------------------------------------|-------------------------|------------------------------|

|               | Interface Blocks                                                 |                         |                              |

| Input E       | Buffers                                                          |                         |                              |

| FI01          | Input buffer, CMOS in                                            | =                       | 12/6                         |

| Outpu         | t Buffers                                                        |                         |                              |

| FO01          | Output buffer, CMOS out                                          | 4                       | 8/5                          |

| FO02          |                                                                  | 8                       | 16/9                         |

| FO03          |                                                                  | 12                      | 16/9                         |

| B007          | Output buffer, CMOS 3-state out                                  | 8                       | 24/15                        |

| Open          | Drain Output Buffers                                             |                         |                              |

| EXT1          | Output buffer, N-ch open drain                                   | 4                       | 8/4                          |

|               |                                                                  |                         |                              |

| Bi-dire       | ectional I/O Buffers                                             |                         |                              |

| B001          | I/O buffer, CMOS in, CMOS 3-state out 50 k $\Omega$ pull-up res. | 8                       | 36/21                        |

### **Function Blocks - Normal Power**

| Inverter (F/O = 25) (FT)<br>Inverter (F/O = 25) (FT)<br>Inverter (x3)<br>Inverter (x4)<br>Inverter (x5)                                              | 4/3<br>8/5<br>-/1                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                      |                                                                                                                                                                                                                         |

| Non-inverting buffer (F/O = 25) (FT)<br>Non-inverting buffer (F/O = 51) (FT)<br>Non-inverting buffer<br>Non-inverting buffer<br>Non-inverting buffer | 8/5<br>12/7<br>-/9                                                                                                                                                                                                      |

|                                                                                                                                                      |                                                                                                                                                                                                                         |

| Delay gate<br>Delay gate                                                                                                                             | 24/13<br>40/22                                                                                                                                                                                                          |

|                                                                                                                                                      | Inverter (F/O = 25) (FT) Inverter (x3) Inverter (x4) Inverter (x5)  Non-inverting buffer (F/O = 25) (FT) Non-inverting buffer (F/O = 51) (FT) Non-inverting buffer Non-inverting buffer Non-inverting buffer Delay gate |

| Block<br>Name                                | Description                                                                                                                                        | Area <sup>1</sup><br>(grids)                |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

|                                              | Function Blocks - Normal Power (C                                                                                                                  | ont)                                        |

| NOR Gat                                      | es                                                                                                                                                 |                                             |

| F202<br>F203<br>F204<br>F208                 | 2-input NOR<br>3-input NOR<br>4-input NOR<br>8-input NOR                                                                                           | 8/5<br>12/7<br>16/10<br>24/18               |

| F222<br>F223<br>F224                         | 2-input NOR, power<br>3-input NOR, power<br>4-input NOR, power                                                                                     | 16/9<br>24/13<br>32/17                      |

| OR Gates                                     | S                                                                                                                                                  |                                             |

| F212<br>F213<br>F214<br>F232<br>F233<br>F234 | 2-input OR 3-input OR 4-input OR 2-input OR, power 3-input OR, power 4-input OR, power                                                             | 8/5<br>12/6<br>12/7<br>12/7<br>16/8<br>16/9 |

| NAND G                                       | ates                                                                                                                                               |                                             |

| F302<br>F303<br>F304<br>F305                 | 2-input NAND<br>3-input NAND<br>4-input NAND<br>5-input NAND                                                                                       | 8/5<br>12/7<br>16/9<br>20/11                |

| F306<br>F308<br>F322<br>F323                 | 6-input NAND<br>8-input NAND<br>2-input NAND, power<br>3-input NAND, power                                                                         | 20/12<br>24/14<br>16/9<br>24/13             |

| F324                                         | 4-input NAND, power                                                                                                                                | 32/17                                       |

| AND Gat                                      | es                                                                                                                                                 |                                             |

| F312<br>F313<br>F314<br>F332<br>F333<br>F334 | 2-input AND 3-input AND 4-input AND 2-input AND, power 3-input AND, power 4-input AND, power                                                       | 8/5<br>12/6<br>12/7<br>12/7<br>16/8<br>16/9 |

| AND-NO                                       | R Gates                                                                                                                                            |                                             |

| F421<br>F422<br>F423<br>F424                 | 2-wide 1-2-input AND-OR inverter<br>3-wide 1-1-2-input AND-OR inverter<br>2-wide 1-3-input AND-OR inverter<br>2-wide 2-2-input AND-OR inverter     | 12/7<br>16/10<br>16/9<br>16/9               |

| F425<br>F426<br>F429<br>F442                 | 3-wide 2-2-2-input AND-OR inverter<br>2-wide 3-3-input AND-OR inverter<br>4-wide 2-2-2-2-input AND-OR inverter<br>2-wide 4-4 input AND-OR inverter | 24/14<br>24/13<br>32/18<br>32/17            |

| F462                                         | 3-wide 1-2-3 input AND-OR inverter                                                                                                                 | 24/14                                       |

| Block<br>Name                                    | Description                                                                                                                                    | Area <sup>1</sup><br>(grids)          | Block<br>Name                | Description                                                                                                                 | Area <sup>1</sup><br>(grids)      |  |  |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--|--|

| Function Blocks - Normal Power (Cont)            |                                                                                                                                                | Function Blocks - Normal Power (Cont) |                              |                                                                                                                             |                                   |  |  |

| OR-NANI                                          | D Gates                                                                                                                                        |                                       | Latches (Cont)               |                                                                                                                             |                                   |  |  |

| F431<br>F432<br>F433<br>F434                     | 2-wide 1-2-input OR-AND inverter<br>3-wide 1-1-2-input OR-AND inverter<br>2-wide 1-3-input OR-AND inverter<br>2-wide 2-2-input OR-AND inverter | 12/7<br>16/10<br>16/9<br>16/9         | F604<br>F605<br>F901<br>F902 | D-latch with G driver low<br>D-latch with G low, Reset low<br>4-bit D-latch<br>8-bit D-latch                                | 24/14<br>28/16<br>80/45<br>152/85 |  |  |

| F435                                             | 2-wide 2-3-input OR-AND inverter                                                                                                               | 20/11                                 | Flip-Flop                    | os                                                                                                                          |                                   |  |  |

| F436<br>F454                                     | 2-wide 3-3-input OR-AND inverter<br>4-wide 2-2-2-input OR-AND inverter                                                                         | 24/13<br>32/18                        | F596<br>F611                 | Synchronous R-S F/F with Set-Reset D-F/F                                                                                    | 44/28<br>32/18                    |  |  |

| Parity Ge                                        | enerators                                                                                                                                      |                                       | F614<br>F617                 | D-F/F with Set-Reset D-F/F with Set-Reset low                                                                               | 40/24<br>40/24                    |  |  |

| F581<br>F582<br><b>EX-OR G</b>                   | 8-bit odd parity generator 8-bit even parity generator sate                                                                                    | 76/48<br>76/48                        | F631<br>F637<br>F641         | D-F/F C low D-F/F C low with Set-Reset low D-F/F, buffered                                                                  | 32/18<br>40/24<br>32/22           |  |  |

| F511                                             | Exclusive-OR                                                                                                                                   | 16/9                                  | F644                         | D-F/F with Set-Reset, buffered                                                                                              | 40/28                             |  |  |

| <b>EX-NOR</b><br>F512                            | Gate Exclusive-NOR                                                                                                                             | 16/9                                  | F647<br>F661<br>F667<br>F714 | D-F/F with Set-Reset low, buffered D-F/F C low, buffered D-F/F C low with Set-Reset low, buffered Toggle F/F with Set-Reset | 40/28<br>32/22<br>40/28<br>36/23  |  |  |

| Adders                                           |                                                                                                                                                |                                       | F717                         | Toggle F/F with Set-Reset low                                                                                               | 36/23                             |  |  |

| F521<br>F523                                     | 1-bit full-adder<br>4-bit binary full-adder                                                                                                    | 36/24<br>128/89                       | F737<br>F744<br>F747         | Toggle low F/F with Set-Reset low Toggle F/F with Set-Reset, buffered Toggle F/F with Set-Reset low, buffered               | 36/23<br>36/27<br>36/27           |  |  |

| Buffers                                          |                                                                                                                                                |                                       | F767                         | Toggle low F/F with Set-Reset low, buffered                                                                                 | 36/27                             |  |  |

| F531<br>F532<br>F533                             | 3-state buffer with Enable<br>3-state buffer with Enable low<br>3-state buffer                                                                 | 20/11<br>20/11<br>36/14               | F771<br>F774<br>F777         | J-K F/F, buffered J-K F/F with Set-Reset, buffered J-K F/F with Set-Reset low, buffered                                     | 40/24<br>48/30<br>48/30           |  |  |

| Decoder:                                         |                                                                                                                                                | 00/14                                 | F781<br>F787                 | J-K F/F C low, buffered J-K F/F C low with Set-Reset low, buffered                                                          | 40/24<br>48/30                    |  |  |

| F561<br>F981<br>F982                             | 2-to-4 decoder 2-to-4 decoder with Enable low 3-to-8 decoder with Enable low                                                                   | 40/24<br>52/31<br>104/60              | F791<br>F792                 | Toggle F/F with Set-Reset and Toggle Enable Toggle low F/F with Set-Reset and Toggle Enable low                             |                                   |  |  |

| Chiff Das                                        | viotoro                                                                                                                                        |                                       | F922                         | 4-bit D-F/F with Reset                                                                                                      | 136/75                            |  |  |

| <b>Shift Reg</b><br>F911<br>F912<br>F913<br>F914 | 4-bit shift register with Reset 4-bit serial/parallel shift register 4-bit parallel shift register with Reset low, Load 4-bit shift register   | 136/75<br>144/80<br>160/92<br>112/61  | F924<br>F615<br>F616<br>S999 | 4-bit D-F/F D-F/F with RB D-F/F with SB 2-to-1 Data Slector (Scan path)                                                     | 112/61<br>-/21<br>-/22<br>-/10    |  |  |

| Multiplex                                        | ers                                                                                                                                            |                                       | Counter                      | s                                                                                                                           |                                   |  |  |

| L655                                             | 2-to-1 multiplexer (no enable/low drive)                                                                                                       | -/7                                   | F961                         | 4-bit synchronous binary counter with Reset low, buffered                                                                   | 240/158                           |  |  |

| F569<br>F570<br>F571                             | 8-to-1 multiplexer<br>4-to-1 multiplexer<br>2-to-1 multiplexer                                                                                 | 72/46<br>36/27<br>20/16               | F962                         | 4-bit synchronous binary up counter with Reset low                                                                          | 152/102                           |  |  |

| F572                                             | Quad 2-to-1 multiplexer                                                                                                                        | 76/35                                 | Compara                      |                                                                                                                             | 400/00                            |  |  |

| Latches                                          |                                                                                                                                                |                                       | F985                         | 4-bit magnitude comparator                                                                                                  | 128/82                            |  |  |

| F595<br>F601                                     | R-S latch<br>D-latch                                                                                                                           | 20/14<br>24/14                        | Miscella                     | neous                                                                                                                       |                                   |  |  |

| F602<br>F603                                     | D-latch with Reset D-latch with Reset low                                                                                                      | 24/15<br>28/16                        | F091                         | H, L level Generator                                                                                                        |                                   |  |  |

| F603                                             | D-latch with Reset low                                                                                                                         | 28/16                                 |                              | ,                                                                                                                           |                                   |  |  |

Note (1): Grids shown are for FT/HD types respectively.

| Block        | Description                                                           | Area <sup>1</sup> | Block          | Description                                                                          | Area <sup>1</sup> |

|--------------|-----------------------------------------------------------------------|-------------------|----------------|--------------------------------------------------------------------------------------|-------------------|

| Name         |                                                                       | (grids)           | Name           | ·                                                                                    | (grids)           |

|              | Function Blocks - Low Power                                           |                   |                | Function Blocks - Low Power (Cont)                                                   |                   |

| Inverters    |                                                                       |                   | Exclusiv       | e-OR                                                                                 |                   |

| L101         | (F/O = 25) (FT)                                                       | 4/2               | L511           | EX-OR                                                                                | 12/8              |

| Buffers      |                                                                       |                   | Exclusiv       | e-NOR                                                                                |                   |

| L111         | Non-inverting buffer (F/O = 25) (FT)                                  | 4/3               | L512           | EX-NOR                                                                               | 12/8              |

| NOR Gat      | es                                                                    |                   | Decoder        |                                                                                      |                   |

| L202         | 2-input NOR                                                           | 4/3               | L561           | 2-to-4 Decoder                                                                       | 24/17             |

| L203         | 3-input NOR                                                           | 8/4               | L981           | 2-to-4 Decoder with Enable                                                           | 68/42             |

| L204         | 4-input NOR                                                           | 8/5               | L982           | 3-to-8 Decoder with Enable                                                           | 68/42             |

| OR Gates     |                                                                       |                   | Multiplex      | ker                                                                                  |                   |

| L212         | 2-input OR                                                            | 8/4               | L571           | 2-to-1 Multiplexer                                                                   | 16/10             |

| L213<br>L214 | 3-input OR<br>4-input OR                                              | 8/5<br>12/6       | L572           | Quad 2-to-1 Multiplexer                                                              | 40/27             |

| NAND Ga      | •                                                                     |                   | Latches        |                                                                                      |                   |

|              |                                                                       |                   | L901           | 4-Bit Latch                                                                          | 48/33             |

| L302<br>L303 | 2-Input NAND<br>3-Input NAND                                          | 4/3<br>8/4        | L902           | 8-Bit Latch                                                                          | 88/61             |

| L303         | 4-Input NAND                                                          | 8/5               | Ol. 16 D -     |                                                                                      |                   |

| L305         | 5-Input NAND                                                          | 12/6              | Shift Reg      | gisters                                                                              |                   |

| L306         | 6-Input NAND                                                          | 8/7               | L911           | 4-Bit Shift Register with Reset                                                      | 104/60            |

| 2000         | o input to utb                                                        | 0/1               | L912<br>L913   | 4-Bit Serial/Parallel Shift Register 4-Bit Parallel in Shift Register with Reset Low | 112/60<br>128/80  |

| AND Gate     | es                                                                    |                   | 2010           | 1 Bit 1 drailer in Crime Progressor With Product 2000                                | 120/00            |

| L312         | 2-Input AND                                                           | 8/4               | Flip Flop      | os .                                                                                 |                   |

| L313         | 3-Input AND                                                           | 8/5               | L922           | 4-Bit D-F/F with Reset                                                               | 104/63            |

| L314         | 4-Input AND                                                           | 12/6              | L924           | 4-Bit D-F/F                                                                          | 80/49             |

| AND-NO       | R Gates                                                               |                   | Megafun        | ctions                                                                               |                   |

| L421         | 2-Wide, 1-2-Input AND-OR Inverter                                     | 8/4               | 70108H         | V20HL 8-bit Microprocessor                                                           | TBA               |

| L422         | 3-Wide 1-1-2-Input AND-OR Inverter                                    | 8/5               | 70116H         | V30HL 16-bit Microprocessor                                                          | TBA               |

| L423         | 2-Wide, 1-3-Input AND-OR Inverter                                     | 8/5               | 78350          | 78K3 16-bit Microprocessor                                                           | TBA               |

| L424         | 2-Wide, 2-2-Input AND-OR Inverter                                     | 8/5               | 70008A         | Z80 8-bit Microprocessor                                                             | TBA               |

| L425<br>L426 | 3-Wide, 2-2-2-Input AND-OR Inverter 2-Wide, 3-3-Input AND-OR Inverter | 12/8<br>12/7      | 72065B         | 765 Floppy Disk Controller                                                           | 78,580            |

| L420<br>L429 | 4-Wide, 2-2-2-Input AND-OR Inverter                                   | 16/10             | 71037          | 8237A Programmable DMA Controller                                                    | 31,780            |

| L442         | 2-Wide, 4-4-Input AND-OR Inverter                                     | 12/9              | 71051<br>71054 | 8251A USART<br>8254 Interval Timer                                                   | 17,750<br>16,170  |

| L462         | 3-Wide, 1-2-3-Input AND-OR Inverter                                   | 12/8              | 71055          | 8255A Peripheral Interface                                                           | 9540              |

| OR-NANI      | D Gates                                                               |                   | 71059<br>71088 | 8259A Interrupt Controller<br>8288 System Bus Controller                             | 7510<br>TBA       |

| L431         | 2-Wide, 1-2-Input OR-AND Inverter                                     | 8/4               | 4991A          | Real Time Clock                                                                      | TBA               |

| L432         | 3-Wide, 1-1-2-Input OR-AND Inverter                                   | 8/5               |                |                                                                                      |                   |

| L433         | 2-Wide, 1-3-Input OR-AND Inverter                                     | 8/5               |                |                                                                                      |                   |

| OR-AND       | Gates                                                                 |                   |                |                                                                                      |                   |

| L434         | 2-Wide, 2-2-Input OR-AND Inverter                                     | 8/5               |                |                                                                                      |                   |

| L435         | 2-Wide, 2-3-Input OR-AND Inverter                                     | 12/6              |                |                                                                                      |                   |

| L436         | 2-Wide, 3-3-Input OR-AND Inverter                                     | 12/7              |                |                                                                                      |                   |

| L454         | 4-Wide, 2-2-2-Input OR-AND Inverter                                   | 16/10             |                |                                                                                      |                   |

Note (1): Grids shown are for FT/HD types respectively.

Notes:

Notes:

### **NEC ASIC DESIGN CENTERS**

#### **WEST**

401 Ellis Street

P.O. Box 7241

Mountain View, CA 94039

TEL 415-965-6533 FAX 415-965-6788

One Embassy Centre 9020 S.W. Washington Square Road, Suite 400 Tigard, OR 97223

TEL 503-671-0177 FAX 503-643-5911

#### SOUTH CENTRAL/SOUTHEAST

16475 Dallas Parkway, Suite 380 Dallas, TX 75248

TEL 972-250-4522 FAX 972-931-8680

Research Triangle Park 2000 Regency Parkway, Suite 455 Cary, NC 27511

TEL 919-460-1890 FAX 919-469-5926

### NORTH CENTRAL/NORTHEAST

One Natick Executive Park Natick, MA 01760

TEL 508-655-8833 FAX 508-653-2915

Greenspoint Tower 2800 W. Higgins Road, Suite 765 Hoffman Estates, IL 60195

TEL 708-519-3945 FAX 708-882-7564

### THIRD-PARTY DESIGN CENTERS

### SOUTH CENTRAL/SOUTHEAST

Koos Technical Services, Inc. 385 Commerce Way, Suite 101 Longwood, FL 32750

TEL 407-260-8727 FAX 407-260-6227

Integrated Silicon Systems Inc.

2222 Chapel Hill Nelson Highway Durham,

NC 27713

TEL 919-361-5814 FAX 919-361-2019

For literature, call toll-free 7 a.m. to 6 p.m. Pacific time:

1-800-366-9782

or FAX your request to: 1-800-729-9288

CORPORATE HEADQUARTERS 2880 Scott Boulevard

P.O. Box 58062 Santa Clara, CA 95052 TEL 408-588-6000 No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics Inc. (NECEL). The information in this document is subject to change without notice. ALL DEVICES SOLD BY NECEL ARE COVERED BY THE PROVISIONS APPEARING IN NECEL TERMS AND CONDITIONS OF SALES ONLY. INCLUDING THE LIMITATION OF LIABILITY, WARRANTY, AND PATENT PROVISIONS. NECEL makes no warranty, express, statutory, implied or by description, regarding information set forth herein or regarding the freedom of the described devices from patent infringement. NECEL assumes no responsibility for any errors that may appear in this document. NECEL makes no commitments to update or to keep current information contained in this document. The devices listed in this document are not suitable for use in applications such as, but not limited to, aircraft control systems, aerospace equipment, submarine cables, nuclear reactor control systems and life support systems. "Standard" quality grade devices are recommended for computers, office equipment, communication equipment, test and measurement equipment, machine tools, industrial robots, audio and visual equipment, and other consumer products. For automotive and transportation equipment, traffic control systems, anti-disaster and anti-crime systems, it is recommended that the customer contact the responsible NECEL salesperson to determine the reliability requirements for any such application and any cost adder. NECEL does not recommend or approve use of any of its products in life support devices or systems or in any application where failure could result in injury or death. If customers wish to use NECEL devices in applications not intended by NECEL, customer must contact the responsible NECEL sales people to determine NECEL's willingness to support a given application.